# Semantics and tools for low-level concurrent programming

#### January, 14-18 2013

#### Mark Batty

#### U. Cambridge

# Formalisation of the C11/C++11 concurrency model

Discovered and fixed several unsoundness in the standard

#### Techniques to find bugs, or prove correctness, of graphics processing unit (GPU) kernels

Software performance optimisation for multicore processors

#### Alastair Donaldson

#### Imperial College

# Martin Vechev

#### ETH Zurich

#### Software reliability

# Program analysis and synthesis for building robust systems

Applications to concurrent algorithms

# Francesco Zappa Nardelli

INRIA

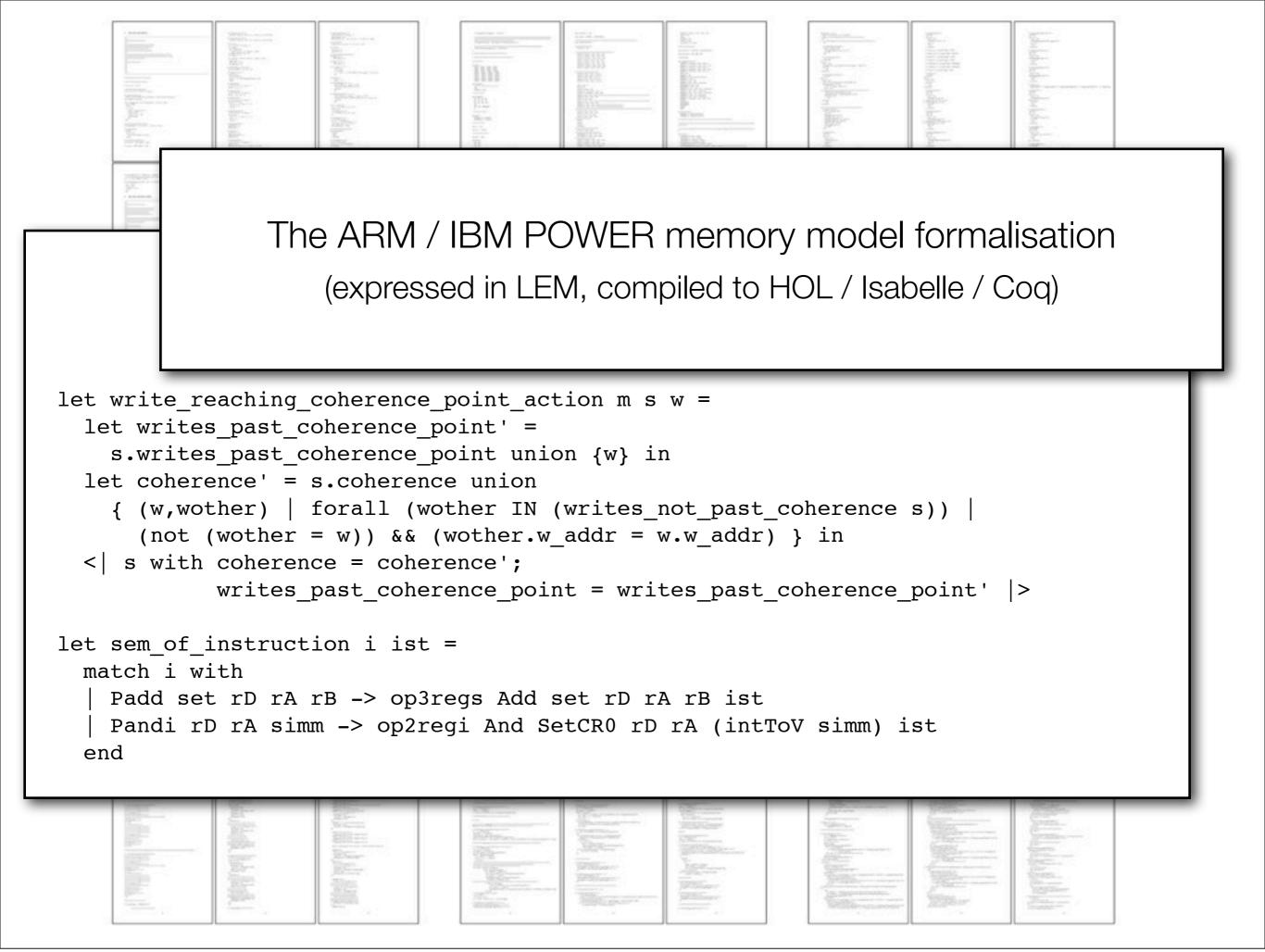

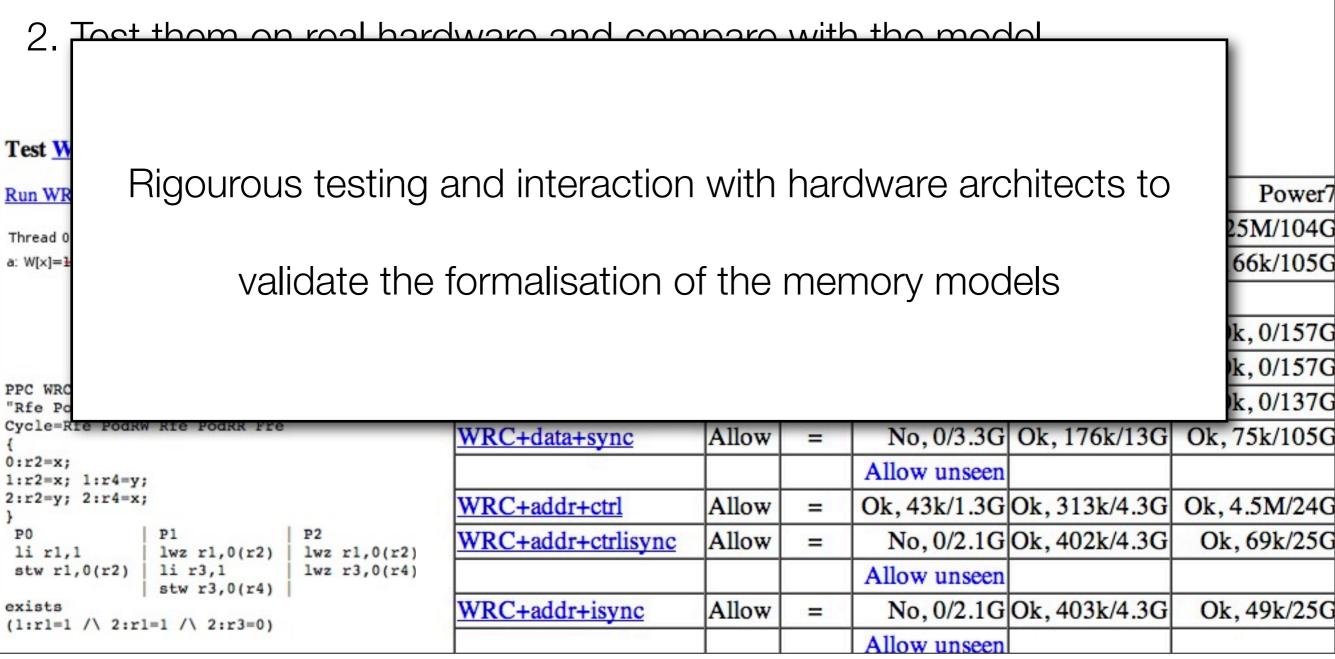

Formalisation of hardware and programming language memory models

Compilation and concurrency

#### **Optional exam: Friday 2pm-3.30pm**

# Do not forget your laptop for the TD sessions.

#### Thursday afternoon: free

#### Do not forget the presence sheet

#### Do not forget the presence sheet

# Semantics and tools for low-level concurrent programming

#### Mark Batty U. Cambridge

#### Alastair Donaldson Imperial College

Martin Vechev ETH Zurich

INRIA

Francesco Zappa Nardelli

# concurrent programming

excerpt from Linux spinlock.c

```

void __lockfunc _##op##_lock(locktype##_t *lock)

ł

for (;;) {

preempt disable();

if (<u>likely(_raw_##op##_trylock(lock</u>)))

break;

preempt enable();

if (!(<u>lock</u>)->break lock)

(lock)->break lock = 1;

while (!op##_can_lock(lock) && (lock)->break_lock)

_raw_##op##_relax(&lock->raw_lock);

}

(lock)->break_lock = 0;

}

/**

* LazyInitRace

excerpt from Linux spinlock.c

* Race condition in lazy initialization

* @author Brian Goetz and Tim Peierls

*/

@NotThreadSafe

public class LazyInitRace {

private ExpensiveObject instance = null;

public ExpensiveObject getInstance() {

if (instance == null)

instance = new ExpensiveObject();

return instance;

}

excerpt from

}

www.javaconcurrencyinpractice.com

class ExpensiveObject { }

```

```

ResourceResponse response;

52

53

unsigned long identifier = std::numeric limits<unsigned long>::max();

54

if (document->frame())

55

identifier = document->frame()->loader()->loadResourceSynchronously(request, storedCredentials, error, response

56

57

// No exception for file:/// resources, see <rdar://problem/4962298>.

58

// Also, if we have an HTTP response, then it wasn't a network error in fact.

59

if (!error.isNull() && !request.url().isLocalFile() && response.httpStatusCode() <= 0) {

60

client.didFail(error);

61

return;

62

}

63

// FIXME: This check along with the one in willSendRequest is specific to xhr and

64

65

// should be made more generic.

66

if (sameOriginReguest && !document->securityOrigin()->canReguest(response.url())) {

67

client.didFailRedirectCheck();

68

return;

69

}

70

71

client.didReceiveResponse(response);

72

73

const char* bytes = static_cast<const char*>(data.data());

74

int len = static cast<int>(data.size());

75

client.didReceiveData(bytes, len);

76

77

client.didFinishLoading(identifier);

78 }

70

*/

```

```

@NotThreadSafe

public class LazyInitRace {

private ExpensiveObject instance = null;

public ExpensiveObject getInstance() {

if (instance == null)

instance = new ExpensiveObject();

return instance;

}

}

class ExpensiveObject { }

```

excerpt from www.javaconcurrencyinpractice.com

| ResourceResponse response;                                                                                            |                |

|-----------------------------------------------------------------------------------------------------------------------|----------------|

| unsigned long identifier = std::numeric_limits <unsigned long="">::max();</unsigned>                                  |                |

| if (document->frame())                                                                                                |                |

| <pre>identifier = document-&gt;frame()-&gt;loader()-&gt;loadResourceSynchronously(request, storedCredentials, e</pre> | rror, response |

| // No                                                                                                                 |                |

| // NO<br>// Als                                                                                                       |                |

| if (le                                                                                                                |                |

|                                                                                                                       |                |

| in practice                                                                                                           |                |

| }                                                                                                                     |                |

|                                                                                                                       |                |

| sequential code, interaction via <i>shared memory</i> , some OS calls.                                                |                |

|                                                                                                                       |                |

| if (sa                                                                                                                |                |

| ci<br>relibuarias reastructuras chatrasticus (a errease ere reasiner)                                                 |                |

| Libraries may provide some abstractions (e.g. message passing).                                                       |                |

| However, somebody must still implement these libraries. And                                                           |                |

| client                                                                                                                |                |

|                                                                                                                       |                |

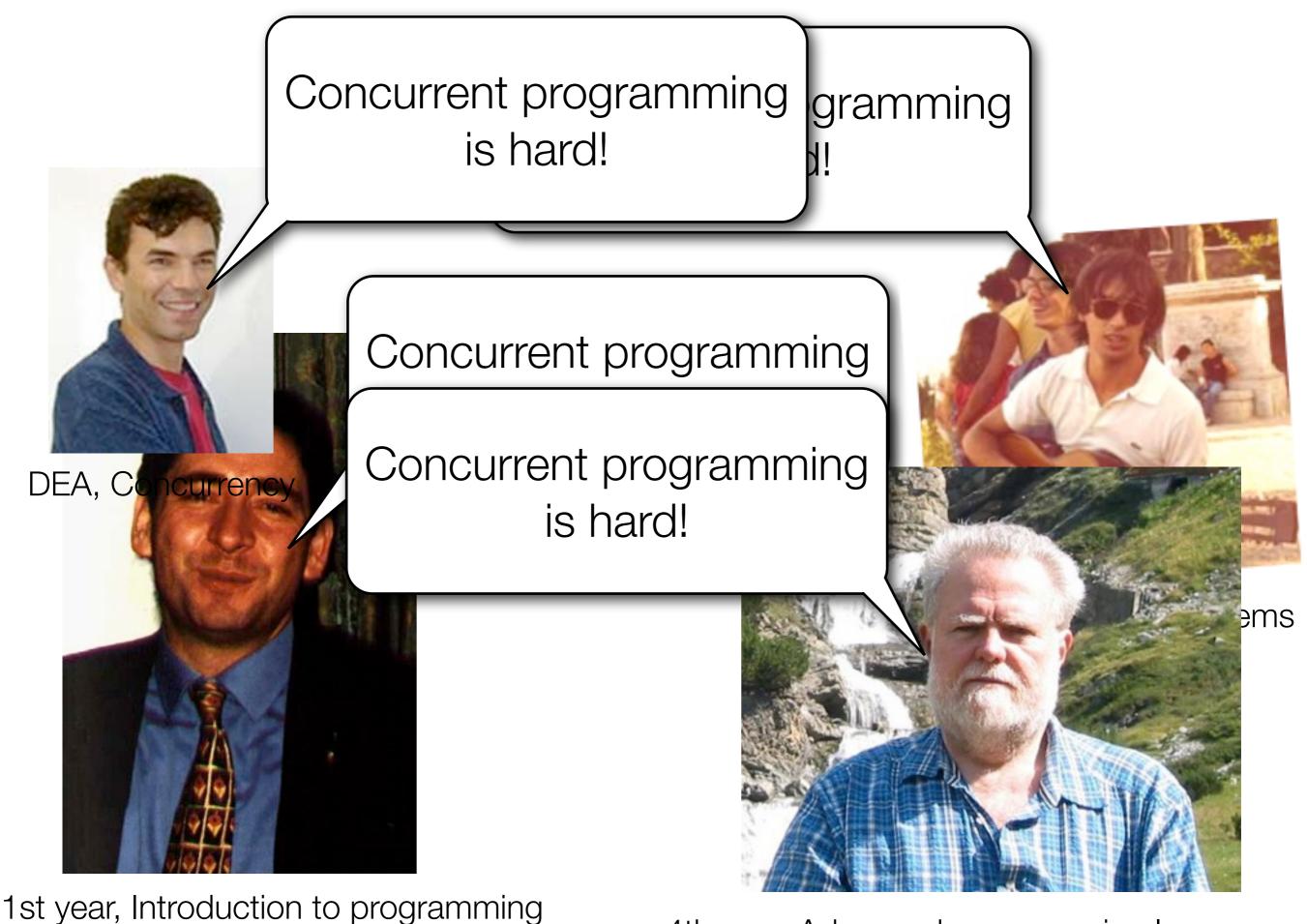

| Const<br>Drogramming is hard                                                                                          |                |

| int 1 Programming is hard:                                                                                            |                |

| subtle algorithms, awful corner cases.                                                                                |                |

| client                                                                                                                |                |

|                                                                                                                       |                |

| Testing is hard:                                                                                                      |                |

|                                                                                                                       | :+             |

| some behaviours are observed rarely and difficult to reproduce.                                                       | <u>n</u>       |

| ,                                                                                                                     |                |

|                                                                                                                       |                |

| Warm-up: let's implement a shared stack!                                                                              |                |

|                                                                                                                       |                |

|                                                                                                                       |                |

| excerpt from                                                                                                          |                |

|                                                                                                                       |                |

| www.javaconcurrencyinpractice.com                                                                                     |                |

| <pre>class ExpensiveObject { }</pre>                                                                                  |                |

|                                                                                                                       |                |

#### Setup

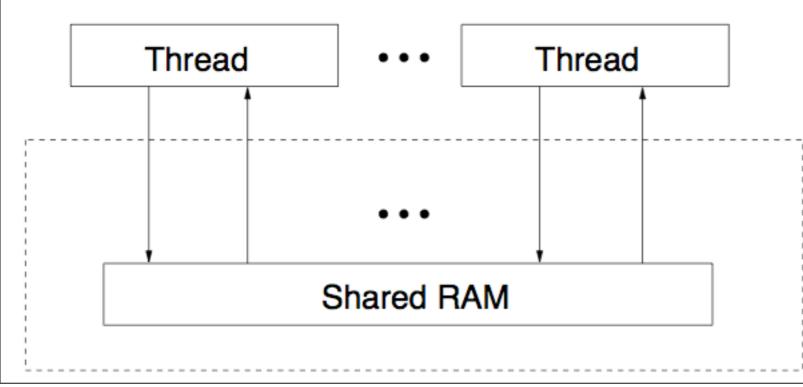

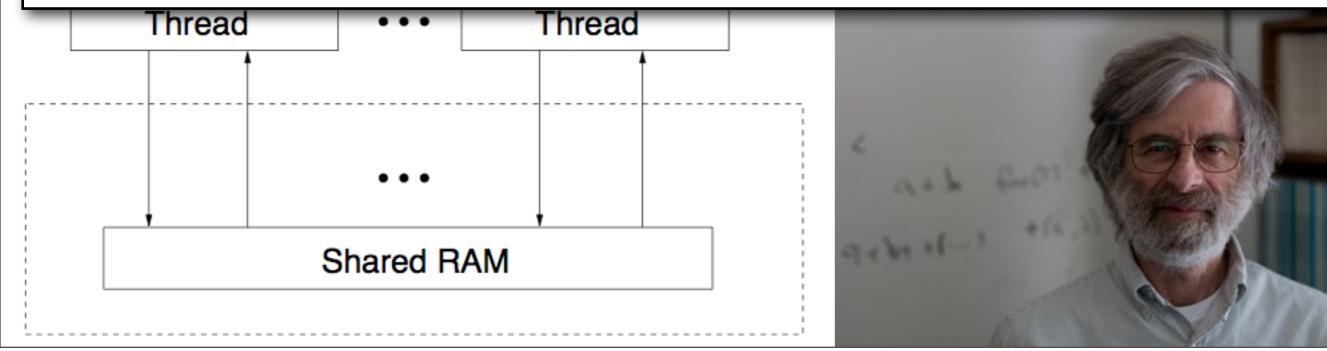

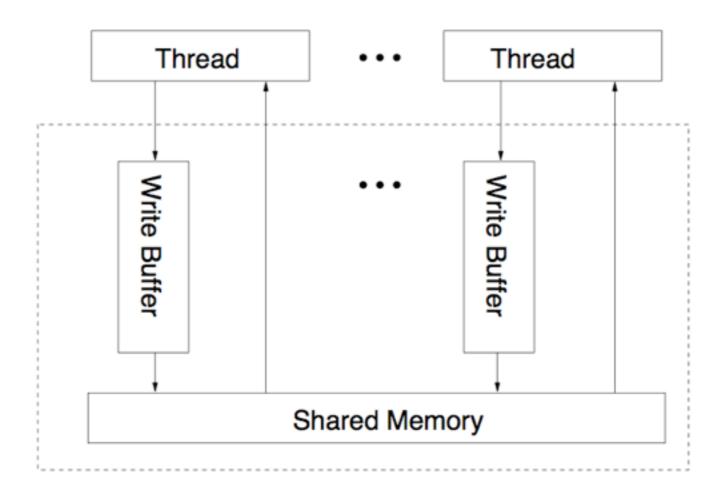

A program is composed by *threads* that communicate by writing and reading in a *shared memory.* No assumptions about the relative speed of the threads.

In this example we will use a *mild variant* of the C programming language:

- local variables: x, y, ...

(allocated on the stack, local to each thread)

- global variables: Top, H, ... (allocated on the heap, shared between threads)

- data structures: arrays H[i], records n = t->tl, ...

- an atomic *compare-and-swap* operation (e.g. CMPXCHG on x86):

```

bool CAS (value_t *addr, value_t exp, value_t new) {

atomic {

if (*addr == exp) then { *addr = new; return true; }

else return false;

}}

```

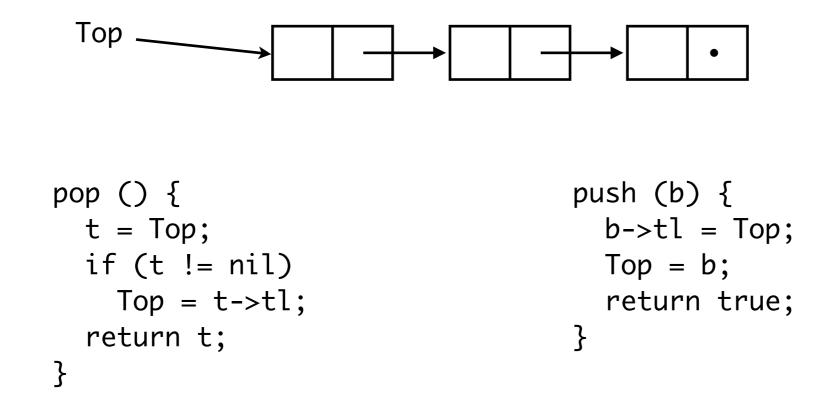

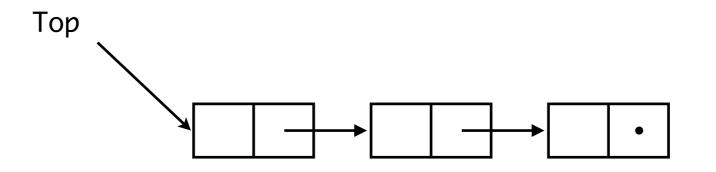

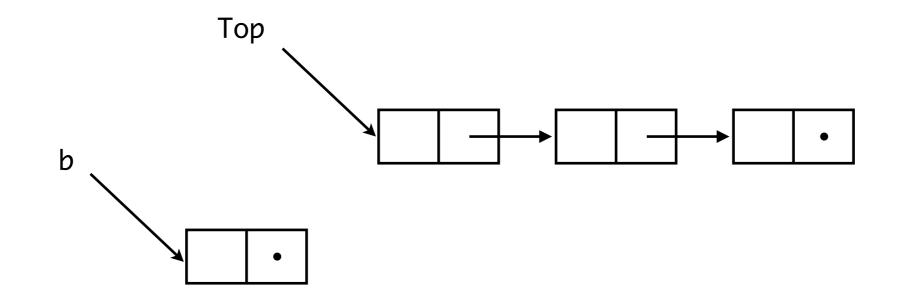

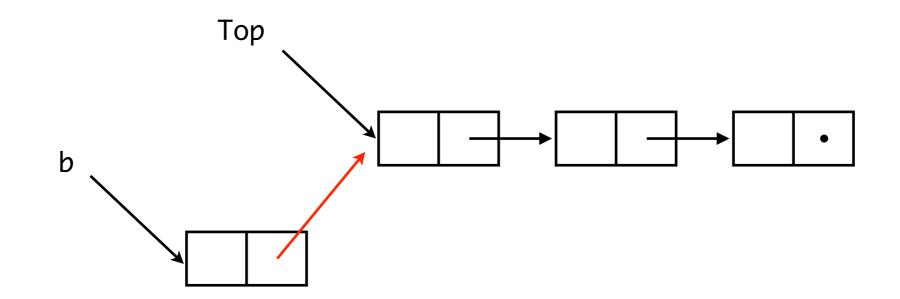

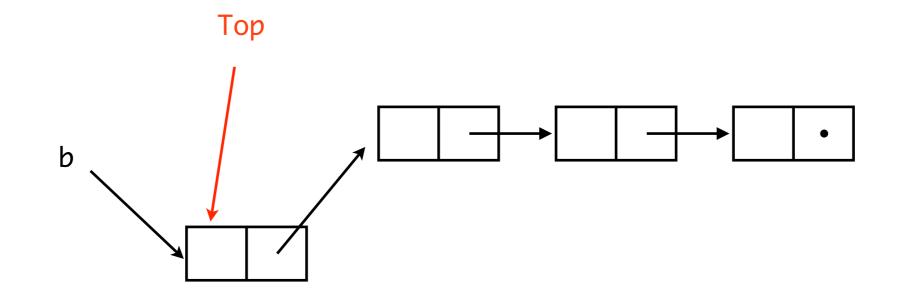

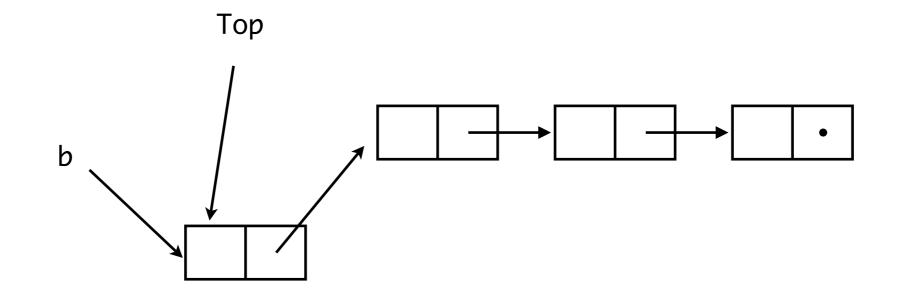

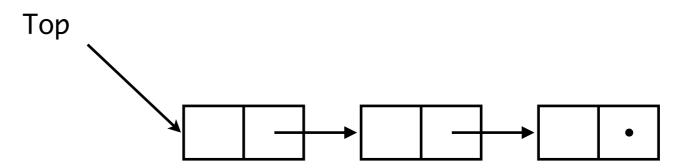

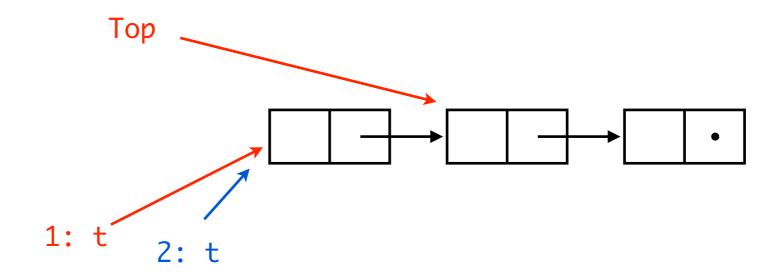

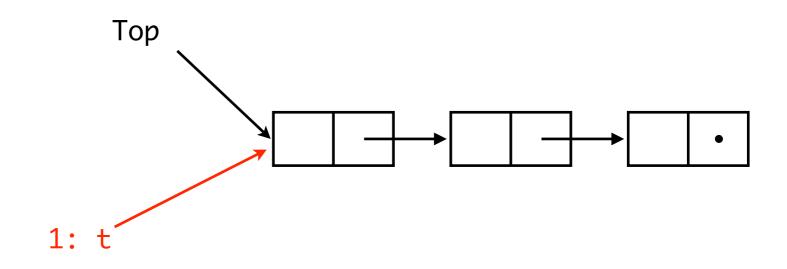

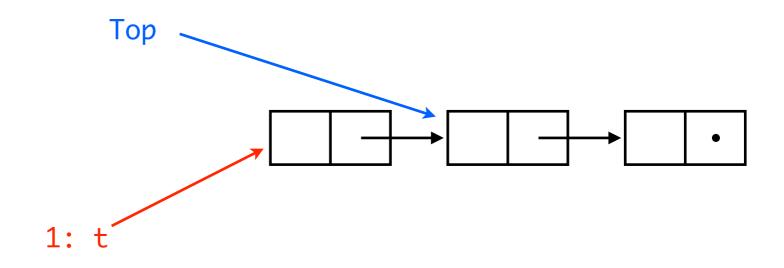

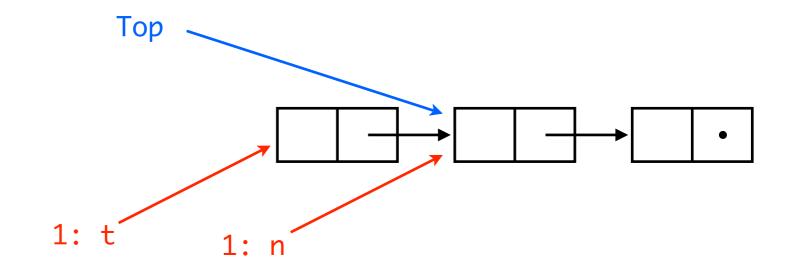

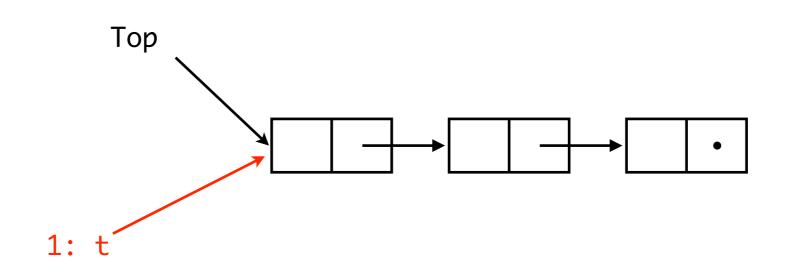

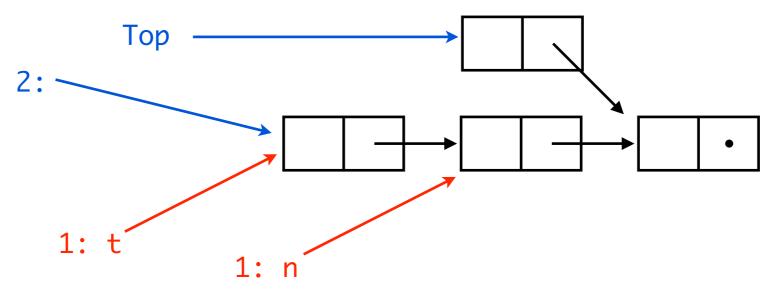

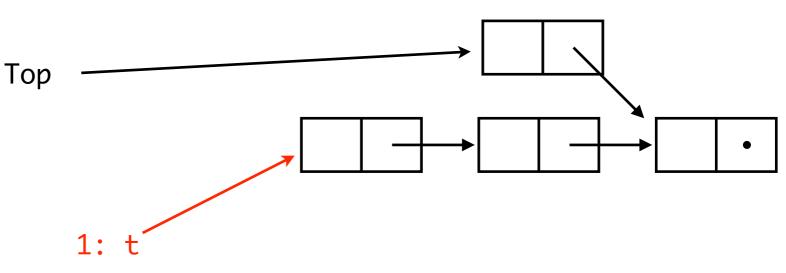

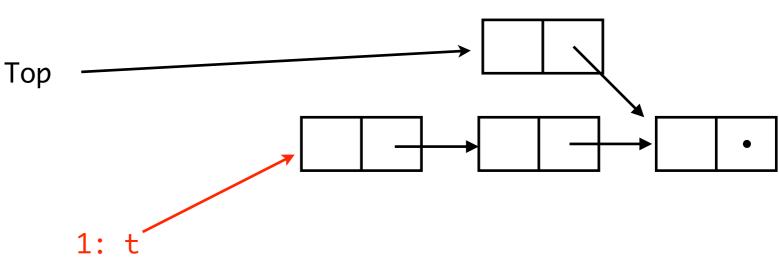

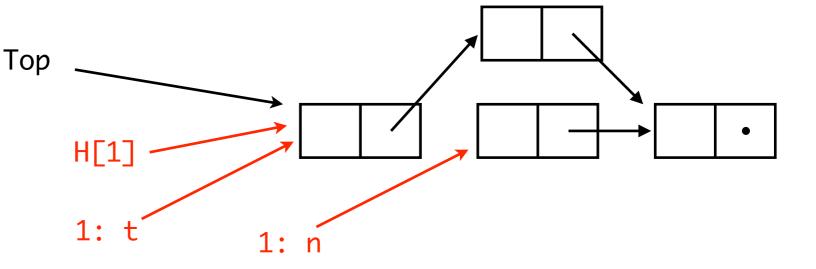

#### A stack

We implement a stack using a list living in the heap:

• each entry of the stack is a record of two fields:

typedef struct entry { value hd; entry \*tl } entry

• the top of the stack is pointed by Top.

#### A sequential stack: demo

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

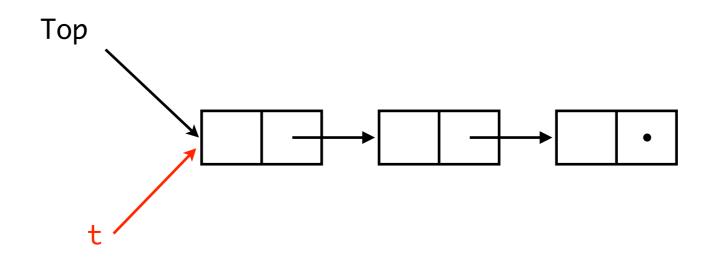

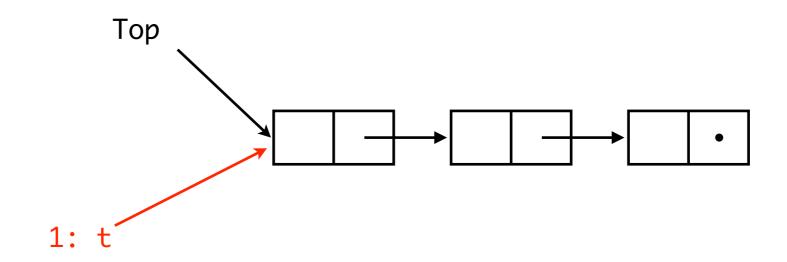

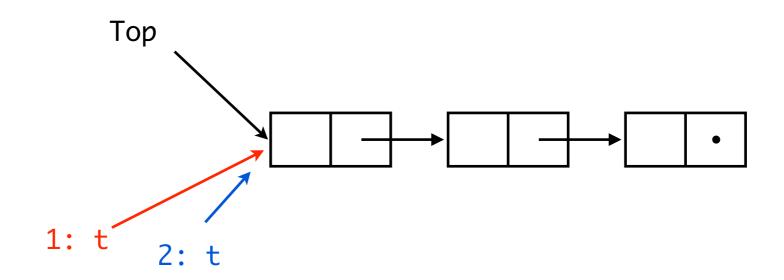

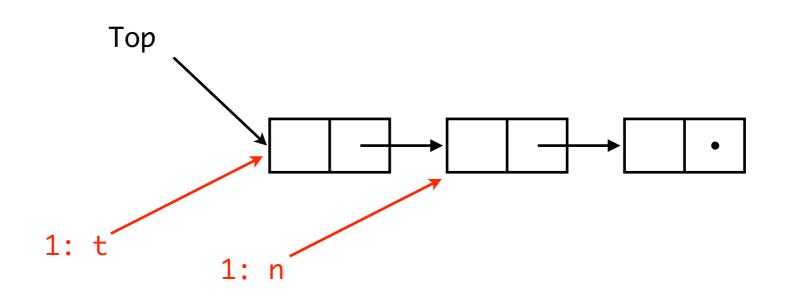

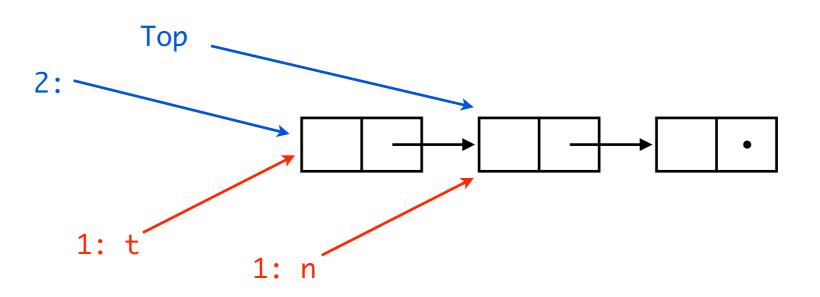

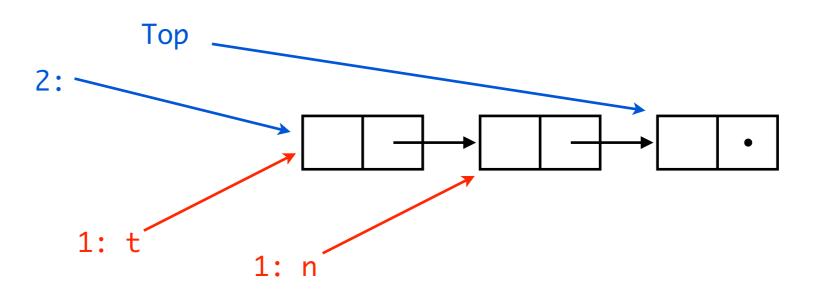

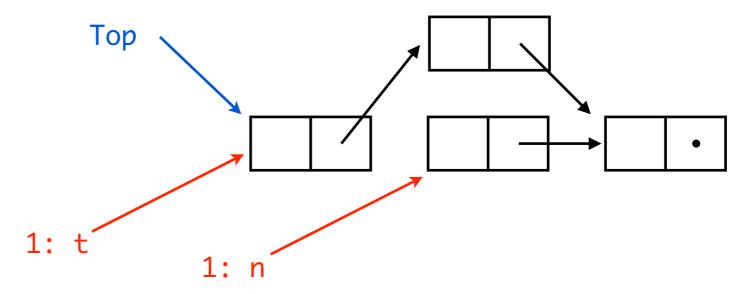

# A sequential stack: pop()

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

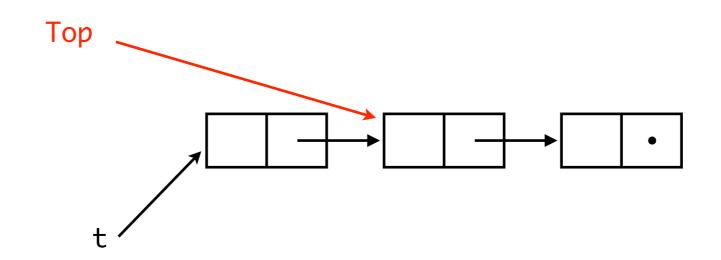

# A sequential stack: pop()

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

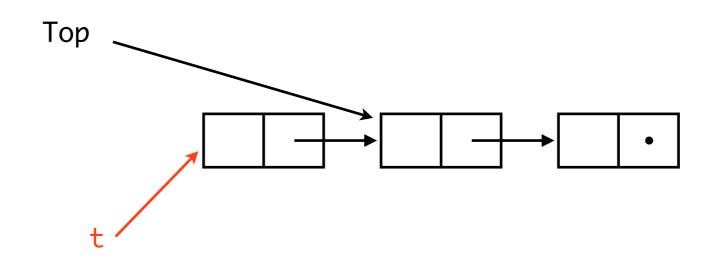

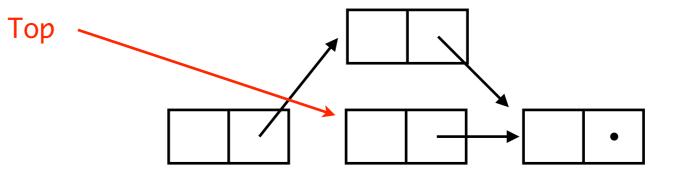

# A sequential stack: pop()

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

```

pop ( ) {

t = Top;

if (t != nil)

Top = t->tl;

return t;

}

```

```

push (b) {

b->tl = Top;

Top = b;

return true;

}

```

Imagine that two threads invoke pop() concurrently...

...the two threads might pop the same entry!

```

pop ( ) {

while (true) {

t = Top;

if (t == nil) break;

n = t->tl;

if CAS(&Top,t,n) break;

}

return t;

}

```

```

push (b) {

while (true) {

t = Top;

b->tl = t;

if CAS(&Top,t,b) break;

}

return true;

}

```

```

push (b) {

pop () {

while (true) {

while (true) {

t = Top;

t = Top;

b \rightarrow tl = t;

if (t == nil) break;

if CAS(&Top,t,b) break;

n = t \rightarrow tl;

}

if CAS(&Top,t,n) break;

return true;

}

}

return t;

}

```

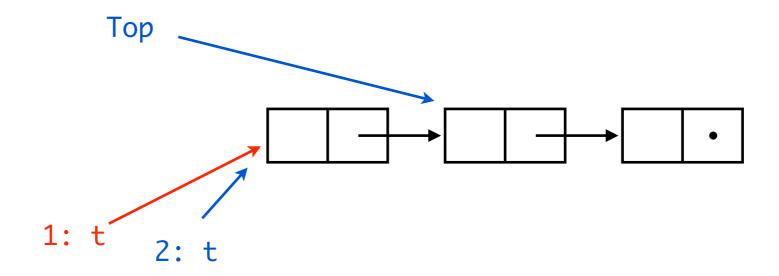

Two concurrent pop() now work fine...

```

push (b) {

pop () {

while (true) {

while (true) {

t = Top;

t = Top;

b \rightarrow tl = t;

if (t == nil) break;

if CAS(&Top,t,b) break;

n = t \rightarrow tl;

}

if CAS(&Top,t,n) break;

return true;

}

}

return t;

}

```

Two concurrent pop() now work fine...

```

push (b) {

pop () {

while (true) {

while (true) {

t = Top;

t = Top;

b \rightarrow tl = t;

if (t == nil) break;

if CAS(&Top,t,b) break;

n = t \rightarrow tl;

}

if CAS(&Top,t,n) break;

return true;

}

}

return t;

}

```

Two concurrent pop() now work fine...

The CAS of Th. 1 fails.

# The ABA problem

```

push (b) {

pop ( ) {

while (true) {

while (true) {

t = Top;

t = Top;

b \rightarrow tl = t;

if (t == nil) break;

if CAS(&Top,t,b) break;

n = t \rightarrow tl;

}

if CAS(&Top,t,n) break;

return true;

}

}

return t;

}

```

Th 1 starts popping...

# The ABA problem

```

push (b) {

pop ( ) {

while (true) {

while (true) {

t = Top;

t = Top;

b \rightarrow tl = t;

if (t == nil) break;

if CAS(&Top,t,b) break;

n = t \rightarrow tl;

}

if CAS(&Top,t,n) break;

return true;

}

}

return t;

}

```

Th 1 starts popping...

### The ABA problem

```

push (b) {

pop ( ) {

while (true) {

while (true) {

t = Top;

t = Top;

b \rightarrow tl = t;

if (t == nil) break;

if CAS(&Top,t,b) break;

n = t \rightarrow tl;

}

if CAS(&Top,t,n) break;

return true;

}

}

return t;

}

```

Th 2 pops...

```

push (b) {

pop ( ) {

while (true) {

while (true) {

t = Top;

t = Top;

b \rightarrow tl = t;

if (t == nil) break;

if CAS(&Top,t,b) break;

n = t \rightarrow tl;

}

if CAS(&Top,t,n) break;

return true;

}

}

return t;

}

```

Th 2 pops again...

```

pop ( ) {

while (true) {

t = Top;

if (t == nil) break;

n = t->tl;

if CAS(&Top,t,n) break;

}

return t;

}

```

```

push (b) {

while (true) {

t = Top;

b->tl = t;

if CAS(&Top,t,b) break;

}

return true;

}

```

Th 2 pushes a new node...

```

push (b) {

pop () {

while (true) {

while (true) {

t = Top;

t = Top;

b \rightarrow tl = t;

if (t == nil) break;

if CAS(&Top,t,b) break;

n = t \rightarrow tl;

}

if CAS(&Top,t,n) break;

return true;

}

}

return t;

}

```

Th 2 pushes the old head of the stack...

```

pop ( ) {

while (true) {

t = Top;

if (t == nil) break;

n = t->tl;

if CAS(&Top,t,n) break;

}

return t;

}

```

```

push (b) {

while (true) {

t = Top;

b->tl = t;

if CAS(&Top,t,b) break;

}

return true;

}

```

Th 1 corrupts the stack...

#### The hazard pointers methodology

Michael adds to the previous algorithm *a global array* H of hazard pointers:

- thread i alone is allowed to write to element H[i] of the array;

- any thread can read any entry of H.

The algorithm is then modified:

- before popping a cell, a thread puts its address into its own element of H.

This entry is cleared only if CAS succeeds or the stack is empty;

- before pushing a cell, a thread checks to see whether it is pointed to from any element of H. If it is, push is delayed.

# Michael's algorithm, simplified

```

push (b) {

for (n = 0; n < no_threads, n++)

if (H[n] == b) return false;

while (true) {

t = Top;

b->tl = t;

if CAS(&Top,t,b) break;

}

return true;

}

```

# Michael's algorithm, simplified

```

pop ( ) {

while (true) {

atomic { t = Top;

H[tid] = t; };

if (t == nil) break;

n = t->tl;

if CAS(&Top,t,n) break;

}

H[tid] = nil;

return t;

}

```

```

push (b) {

for (n = 0; n < no_threads, n++)

if (H[n] == b) return false;

while (true) {

t = Top;

b->tl = t;

if CAS(&Top,t,b) break;

}

return true;

}

```

Th 2 cannot push the old head, because Th 1 has an hazard pointer on it...

# Key properties of Michael's simplified algorithm

- A node can be added to the hazard array only if it is reachable through the stack;

- a node that has been popped is not reachable through the stack;

- a node that is unreachable in the stack and that is in the hazard array cannot be added to the stack;

- while a node is reachable and in the hazard array, it has a constant tail.

These are a good example of the properties we might want to state and prove about a concurrent algorithm.

```

push (b) {

pop ( ) {

for (n = 0; n < no_{threads}, n++)

while (true) {

if (H[n] == b) return false;

t = Top;

while (true) {

H[tid] = t;

t = Top;

if (t == nil) break;

b \rightarrow tl = t;

n = t -> tl;

if CAS(&Top,t,b) break;

if CAS(&Top,t,n) break;

}

}

return true;

H[tid] = nil;

}

return t;

}

Тор

Th 1 copies Top...

```

1:

```

pop ( ) {

while (true) {

t = Top;

H[tid] = t;

if (t == nil) break;

n = t->tl;

if CAS(&Top,t,n) break;

}

H[tid] = nil;

return t;

}

```

```

push (b) {

for (n = 0; n < no_threads, n++)

if (H[n] == b) return false;

while (true) {

t = Top;

b->tl = t;

if CAS(&Top,t,b) break;

}

return true;

}

```

Th 2 pops twice, and pushes a new node...

```

pop ( ) {

while (true) {

t = Top;

H[tid] = t;

if (t == nil) break;

n = t->tl;

if CAS(&Top,t,n) break;

}

H[tid] = nil;

return t;

}

```

```

push (b) {

for (n = 0; n < no_threads, n++)

if (H[n] == b) return false;

while (true) {

t = Top;

b->tl = t;

if CAS(&Top,t,b) break;

}

return true;

}

```

Th 2 starts pushing the old head, and is halfway in the for loop...

```

pop ( ) {

while (true) {

t = Top;

H[tid] = t;

if (t == nil) break;

n = t->tl;

if CAS(&Top,t,n) break;

}

H[tid] = nil;

return t;

}

```

```

push (b) {

for (n = 0; n < no_threads, n++)

if (H[n] == b) return false;

while (true) {

t = Top;

b->tl = t;

if CAS(&Top,t,b) break;

}

return true;

}

```

Th 1 sets its hazard pointer... but Th 2 might not see the hazard pointer of Th 1!

#### Michael shared stack

```

push (b) {

pop ( ) {

for (n = 0; n < no_{threads}, n++)

while (true) {

if (H[n] == b) return false;

t = Top;

while (true) {

if (t == nil) break;

t = Top;

H[tid] = t;

b \rightarrow tl = t;

if (t != Top) break;

if CAS(&Top,t,b) break;

n = t \rightarrow tl;

}

if CAS(&Top,t,n) break;

return true;

}

}

H[tid] = nil;

return t;

}

Trust me: if we validate t against the

Top pointer before reading t->t1, we

get a correct algorithm.

```

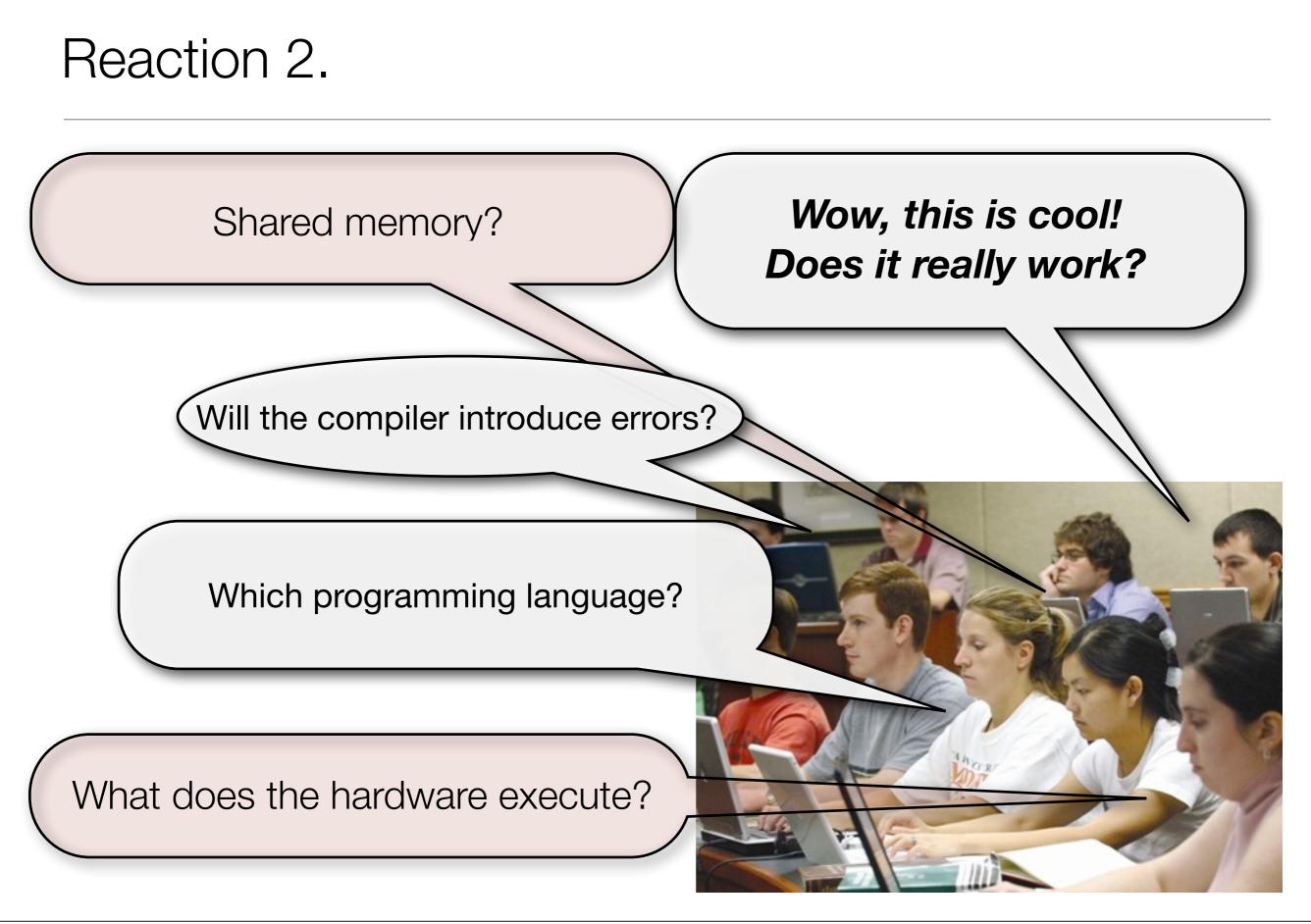

# Reaction 1.

That algorithm is insane... I will never use it in my everyday programming.

# Reaction 1.

Yes, you will! Michael algorithms are part of java.util.concurrent.

# Reaction 1.

# Welcome !!!

- 1. Shared-memory concurrency, from hardware to programming languages

- 2. Machine assisted concurrent programming

- 3. GPU kernels

What does the hardware execute?

#### **Optional exam: Friday 2pm-3.30pm**

# Do not forget your laptop for the TD sessions.

#### Thursday afternoon: free

#### (from Wikipedia)

In computer hardware, **shared memory** refers to a (typically) large block of random access memory (RAM) that can be accessed by several different central processing units (CPUs) in a multiple-processor computer system.

A shared memory system is relatively easy to program since all processors share a single view of data and the communication between processors can be as fast as memory accesses to a same location. The issue with shared memory systems is that many CPUs need fast access to memory and will likely cache memory, which has two complications:

- CPU-to-memory connection becomes a bottleneck. Shared memory computers cannot scale very well. Most of them have ten or fewer processors.

- Cache coherence: Whenever one cache is updated with information that may be used by other processors, the change needs to be reflected to the other processors, otherwise the different processors will be working with incoherent data (see cache coherence and memory coherence). Such coherence protocols can, when they work well, provide extremely high-performance access to shared information between multiple processors. On the other hand they can sometimes become overloaded and become a bottleneck to performance.

| In computer in (RAM) that can computer systems |                                                                                                                                                                                                                                                                                                    | s memory<br>iple-processor                    |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| A shared me                                    | mory system is relatively easy to program since all processors share a                                                                                                                                                                                                                             | single view of data                           |

| and the commissue v<br>memo                    | all processors share a single view of data                                                                                                                                                                                                                                                         | a same location. The<br>and will likely cache |

| • СР <del>о-ю-п</del>                          | nemory connection becomes a bottleneck. Snared memory computers                                                                                                                                                                                                                                    | cannot scale very                             |

| well. Mos                                      | t of them have ten or fewer processors.                                                                                                                                                                                                                                                            |                                               |

| processo                                       | wherence: Whenever one cache is updated with information that may be<br>rs, the change needs to be reflected to the other processors, otherwise<br>rs will be working with incoherent data (see cache coherence and men<br>re protocols can, when they work well, provide extremely high-performa- | e the different<br>nory coherence). Such      |

|                                                | on between m<br>me a bottlenebottleneck to performance                                                                                                                                                                                                                                             | ə                                             |

### Shared memory

#### (from Wikipedia)

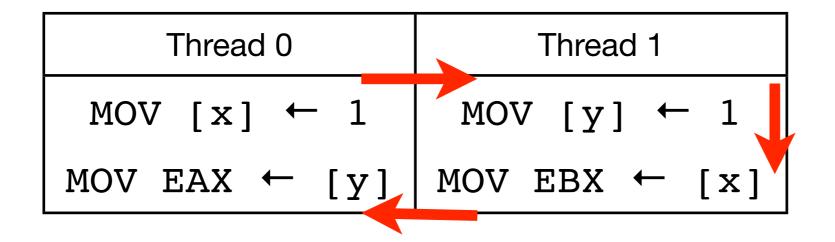

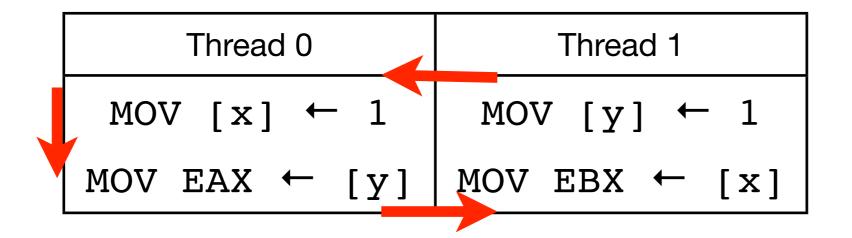

Initial shared memory values: [x]=0 [y]=0

Per-processor registers: EAX EBX

| Thread 0      | Thread 1      |

|---------------|---------------|

| MOV [x] ← 1   | MOV [y] ← 1   |

| MOV EAX ← [y] | MOV EBX ← [x] |

Initial shared memory values: [x]=0 [y]=0

Per-processor registers: EAX EBX

| Thread 0      | Thread 1      |

|---------------|---------------|

| MOV [x] ← 1   | MOV [y] ← 1   |

| MOV EAX ← [y] | MOV EBX ← [x] |

|               |               |

Initial shared memory values: [x]=0 [y]=0

Per-processor registers: EAX EBX

Initial shared memory values: [x]=0 [y]=0

Per-processor registers: EAX EBX

Initial shared memory values: [x]=0 [y]=0

Per-processor registers: EAX EBX

Initial shared memory values: [x]=0 [y]=0

Per-processor registers: EAX EBX

| Thread 0      | Thread 1      |

|---------------|---------------|

| MOV [x] ← 1   | MOV [y] ← 1   |

| MOV EAX ← [y] | MOV EBX ← [x] |

Initial shared memory values: [x]=0 [y]=0

Per-processor registers: EAX EBX

| Thread 0      | Thread 1      |

|---------------|---------------|

| MOV [x] ← 1   | MOV [y] ← 1   |

| MOV EAX ← [y] | MOV EBX ← [x] |

| Thread 0      | Thread 1                 |

|---------------|--------------------------|

| MOV [x] ← 1   | MOV [y] ← 1              |

| MOV EAX ← [y] | MOV EBX $\leftarrow$ [x] |

The possible outcomes should be:

- EAX : 1, EBX : 1

- EAX : 0, EBX : 1

- EAX : 1, EAX : 0

6388 SL95A MALAY 1.866HZ/2M/1866/86

Multiprocessors have a *sequentially consistent* shared memory:

...the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program...

Lamport, 1979.

Multiprocessors have a *sequentially consistent* shared memory:

Properties

- no thread local reordering

- each write becomes visible to all threads at the same time

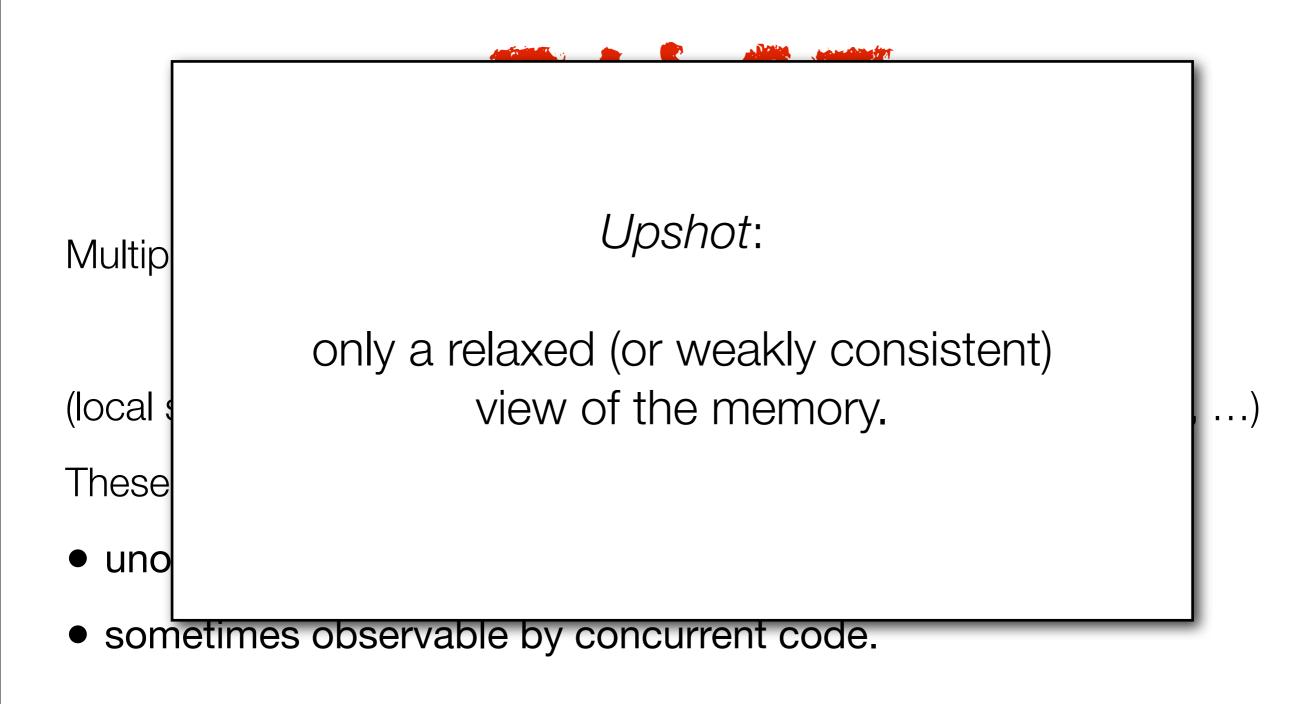

Multiprocessors (and compilers) incorporate many

#### performance optimisations

(local store buffers, shadowing register files, hierarchies of caches, ...)

These are:

- unobservable by single-threaded programs;

- sometimes observable by concurrent code.

### Not new

Multiprocessors since 1964 (Univac 1108A - or Burroughs, in '62)

Relaxed Memory since 1972 (IBM System 370/158MP)

Eclipsed for a long time (except in high-end) by advances in performance:

- transistor counts (continuing)

- clock speed (hit power dissipation limit)

- ILP (hit smartness limit?)

# Mass market multiprocessors since 2005

IBM Power 795 server up to 1024 hardware threads

# Best quad core phone: 4 contenders examined

EARLY VIEW HTC One X vs ZTE Era vs LG Optimus 4X HD vs Huawei Ascend D Quad

# Mass market multiprocessors since 2005

# Best quad core phone: 4 contenders examined

EARLY VIEW HTC One X vs ZTE Era vs LG Optimus 4X HD vs Huawei Ascend D Quad

## But it's hard!

- 1. Real memory models are subtle

- 2. Real memory models differ between architectures

- 3. Real memory models differ between languages

Almost none of the last 40 years' work on verification of concurrent code deals with relaxed memory (new trend in the last few years).

Much of the research on relaxed models does not address real processors and languages (new trend in the last few years).

| 1. I            | Real memory models are subtle                                |

|-----------------|--------------------------------------------------------------|

| 2.              |                                                              |

| 3.              | Industrial processors and language specs<br>are often flawed |

| Alr             | We've looked at the specs of x86, Power, ARM, Java, and C++  |

| CO<br>Mu<br>pro | They all have problems                                       |

|                 |                                                              |

## These lectures

Hardware models

why are industrial specs so often flawed?

focus on x86, with a glimpse of Power/ARM

usable models: x86-TSO, Power

### Programming language models

- 1) defining the semantics of a concurrent programming language

- 2) data-race freedom

- 3) soundness of compiler optimisations

- 4) an in-depth look at C11/C++11

- 1. how to code low-level concurrent datastructures

- 2. how to build concurrency testing and verification tools

- 3. how to specify and test multiprocessors

- 4. how to design and express high-level language definitions

- 5. to discover some ugly monsters still lurking in your multiprocessor / your favorite programming language (despite a lot of efforts)

Concurrent Programming in Java<sup>™</sup>

**Design Principles and Patterns**

## Hardware models

## Architectures

Hardware manufacturers document architectures:

- loose specifications

- claimed to cover a wide range of past and future processor implementations.

Architectures should:

- reveal enough for effective programming;

- without unduly constraining future processor design.

*Examples*: Intel 64 and IA-32 Architectures SDM, AMD64 Architecture Programmer's Manual, Power ISA specification, ARM Architecture Reference Manual, ...

Intel® 64 and IA-32 Architectures Software Developer's Manual VOLUME 3A: System Programming Guide Part 1

In practice

Architectures described by informal prose:

In a multiprocessor system, maintenance of cache consistency may, in rare circumstances, require intervention by system software.

(Intel SDM, november 2006, vol3a, 10-5)

As we shall see, such descriptions are:

1) vague; 2) incomplete; 3) unsound.

Fundamental problem: prose specifications cannot be used to test programs or to test processor implementations.

## Intel 64/IA32 and AMD64 - before Aug. 2007

### Era of Vagueness

A model called Processor Ordering, informal prose.

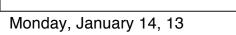

*Example*: Linux kernel mailing list, 20 nov. - 7 déc. 1999 (143 posts). A one-instruction programming question, a microarchitecural debate! *Keywords*: speculation, ordering, causality, retire, cache...

20Nov1999-7Dec1999 (143 posts) Archive Link: "<u>spin\_unlock optimization(i386)</u>" Topics: <u>BSD: FreeBSD, SMP</u> People: <u>Linus Torvalds Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ingo</u>

#### People: Linus Torvalds, Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, In Molnar

Manfred Spraul thought he'd found a way to shave spin\_unlock() down from about 22 ticks for the "lock; btrl \$0,%0" asm code, to 1 tick for a simple "movl \$0,%0" instruction, a huge gain. Later, he reported that Ingo Molnar noticed a 4% speed-up in a benchmark test, making the optimization very valuable. Ingo also added that the same optimization cropped up in the FreeBSD mailing list a few days previously. But Linus Torvalds poured cold water on the whole thing, saying:

#### It does NOT WORK!

Let the FreBSD people use it, and let them get faster timings. They will crash, eventually.

The window may be small, but if you do this, then suddenly spinlocks aren't reliable any more.

The issue is not writes being issued in-order (although all the Intel CPU books warn you NOT to assume that in-order write behaviour - I bet it won't be the case in the long run).

The issue is that you \_have\_ to have a serializing instruction in order to make sure that the processor doesn't re-order things around the unlock.

For example, with a simple write, the CPU can legally delay a read that happened inside the critical region (maybe it missed a cache line), and get a stale value for any of the reads that \_should\_ have been serialized by the spinlock.

#### spin\_unlock();

spin\_lock();

1 = 07

a = 1; /\* cache miss satisfied, the "a" line is bouncing back and forth \*/

b gets the value 1

a = 0;

and it returns "1", which is wrong for any working spinlock.

### Unlikely? Yes, definitely. Something we are willing to live with as a potential bug in any real kernel? Definitely not.

Manfred objected that according to the *Pentium Processor Family Developers Manual, Vol3, Chapter 19.2 Memory Access Ordering*, "to optimize performance, the Pentium processor allows memory reads to be reordered ahead of buffered writes in most situations. Internally, CPU reads (cache hits) can be reordered around buffered writes. Memory reordering does not occur at the pins, reads (cache miss) and writes appear in-order." He concluded from this that the second CPU would never see the spin\_unlock() before the "b=a" line. Linus agreed that on a Pentium, Manfred was right. However, he quoted in turn from the Pentium Pro manual, "The only enhancement in the PentiumPro processor is the added support for speculative reads and store-buffer forwarding." He explained:

A Pentium is a in-order machine, without any of the interesting speculation wrt reads etc. So on a Pentium you'll never see the problem.

### Note that I actually thought this was a legal optimization, and for a while I had this in the kernel. It crashed. In random ways.

Note that the fact that it does not crash now is quite possibly because of either

we have a lot less contention on our spinlocks these days. That might hide the problem, because the \_spinlock\_ will be fine (the cache coherency still means that the spinlock itself works fine - it's just that it no longer works reliably as an exclusion thing)

the window is probably very very small, and you have to be unlucky to hit it. Faster CPU's, different compilers, whatever.

#### I might be proven wrong, but I don't think I am.

Note that another thing is that yes, "btcl" may be the worst possible thing to use for this, and you might test whether a simpler "xor+xchgl" might be better - it's still serializing because it is locked, but it should be the normal 12 cycles that Intel always seems to waste on serializing instructions rather than 22 cycles.

#### Elsewhere, he gave a potential (though unlikely) exploit:

As a completely made-up example (which will probably never show the problem in real life, but is instructive as an example), imaging running the following test in a loop on multiple CPU's:

int test\_locking(void){

static int a; /\* protected by spinlock \*/

int b;

But a Pentium is also very uninteresting from a SMP standpoint these days. It's just too weak with too little per-CPU cache etc..

This is why the PPro has the MTRR's - exactly to let the core do speculation (a Pentium doesn't need MTRR's, as it won't re-order anything external to the CPU anyway, and in fact won't even re-order things internally).

#### Jeff V. Merkey added:

What Linus says here is correct for PPro and above. Using a mov instruction to unlock does work fine on a 486 or Pentium SMP system, but as of the PPro, this was no longer the case, though the window is so infintesimally small, most kernels don't hit it (Netware 4/5 uses this method but it's spinlocks understand this and the code is writtne to handle it. The most obvious aberrant behavior was that cache inconsistencies would occur randomly. PPro uses lock to signal that the piplines are no longer invalid and the buffers should be blown out.

I have seen the behavior Linus describes on a hardware analyzer, BUT ONLY ON SYSTEMS THAT WERE PPRO AND ABOVE. I guess the BSD people must still be on older Pentium hardware and that's why they don't know this can bite in some cases.

Erich Boleyn, an Architect in an IA32 development group at Intel, also replied to Linus, pointing out a possible misconception in his proposed exploit. Regarding the code Linus posted, Erich replied:

It will always return 0. You don't need "spin\_unlock()" to be serializing.

The only thing you need is to make sure there is a store in "spin\_unlock()", and that is kind of true by the fact that you're changing something to be observable on other processors.

spin\_lock()

a = 1;

mb();

a = 0;

mb();

b = a;

spin\_unlock();

return b;

3

Now, OBVIOUSLY the above always has to return 0, right? All accesses to "a" are inside the spinlock, and we always set it to zero before we read it into "b" and return it. So if we EVER returned anything else, the spinlock would obviously be completely broken, wouldn't you say?

And yes, the above CAN return 1 with the proposed optimization. I doubt you can make it do so in real life, but hey, add another access to another variable in the same cache line that is accessed through another spinlock (to get cacheline ping-pong and timing effects), and I suspect you can make it happen even with a simple example like the above.

The reason it can return 1 quite legally is that your new "spin\_unlock()" isnot serializing any more, so there is very little effective ordering between the two actions

b = a;spin\_unlock();

as they access completely different data (ie no data dependencies in sight). So what you could end up doing is equivalent to

CPU#1 CPU#2 b = a; /\* cache miss, we'll delay this.. \*/

The reason for this is that stores can only possibly be observed when all prior instructions have retired (i.e. the store is not sent outside of the processor until it is committed state, and the earlier instructions are already committed by that time), so the any loads, stores, etc absolutely have to have completed first, cache-miss or not.

#### He went on:

Since the instructions for the store in the spin\_unlock have to have been externally observed for spin\_lock to be aquired (presuming a correctly functioning spinlock, of course), then the earlier instructions to set "b" to the value of "a" have to have completed first.

In general, IA32 is Processor Ordered for cacheable accesses. Speculation doesn't affect this. Also, stores are not observed speculatively on other processors.

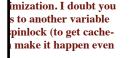

There was a long clarification discussion, resulting in a complete turnaround by Linus:

Everybody has convinced me that yes, the Intel ordering rules \_are\_ strong enough that all of this really is legal, and that's what I wanted. I've gotten sane explanations for why serialization (as opposed to just the simple locked access) is required for the lock() side but not the unlock() side, and that lack of symmetry was what bothered me the most.

Oliver made a strong case that the lack of symmetry can be adequately explained by just simply the lack of symmetry wrt speculation of reads vs writes. I feel comfortable again.

Thanks, guys, we'll be that much faster due to this..

20Nov1999-7Dec1999 (143 posts) Archive Link: "<u>spin\_unlock optimization(i386)</u>" Topics: <u>BSD: FreeBSD, SMP</u> People: <u>Linus Torvalds Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ingo</u>

#### Molnar Manfred Spraul thought he'd found a way to shave spin unlock() down from about

22 ticks for the "lock; btrl \$0,%0" asm code, to 1 tick for a simple "movl \$0,%0" instruction, a huge gain. Later, he reported that Ingo Molnar noticed a 4% speedup in a benchmark test, making the optimization very valuable. Ingo also added that the same optimization cropped up in the FreeBSD mailing list a few days previously. But Linus Torvalds poured cold water on the whole thing, saying:

#### It does NOT WORK!

Let the FreBSD people use it, and let them get faster timings. They will crash, eventually.

The window may be small, but if you do this, then suddenly spinlocks aren't reliable any more.

The issue is not writes being issued in-order (although all the Intel CPU books warn you NOT to assume that in-order write behaviour - I bet it won't be the case in the long run).

The issue is that you \_have\_ to have a serializing instruction in order to make sure that the processor doesn't re-order things around the unlock.

For example, with a simple write, the CPU can legally delay a read that happened inside the critical region (maybe it missed a cache line), and get a stale value for any of the reads that \_should\_ have been serialized by the spinlock.

Note that I actually thought this was a legal optimization, and for a while I had this in the kernel. It crashed. In random ways.

Note that the fact that it does not crash now is quite possibly because of either

we have a lot less contention on our spinlocks these days. That might hide the problem, because the \_spinlock\_ will be fine (the cache coherency still means that the spinlock itself works fine - it's just that it no longer works reliably as an exclusion thing)

the window is probably very very small, and you have to be unlucky to hit it. Faster CPU's, different compilers, whatever.

I might be proven wrong, but I don't think I am.

Note that another thing is that yes, "btcl" may be the worst possible thing to use for this, and you might test whether a simpler "xor+xchgl" might be better - it's still serializing because it is locked, but it should be the normal 12 cycles that Intel always seems to waste on serializing instructions rather than 22 cycles.

Elsewhere, he gave a potential (though unlikely) exploit:

As a completely made-up example (which will probably never show the problem in real life, but is instructive as an example), imaging running the following test in a loop on multiple CPU's:

int test\_locking(void){

static int a; /\* protected by spinlock \*/

int b;

spin\_lock()

a = 1;

mb();

a = 0;

mb();

b = a;

spin\_unlock();

return b;

Now, OBVIOUSLY the above always has to return 0, right? All accesses to "a" are inside the spinlock, and we always set it to zero before we read it into "b" and return it. So if we EVER returned anything else, the spinlock would obviously be completely broken, wouldn't you say?

And yes, the above CAN return 1 with the proposed optimization. I doubt you can make it do so in real life, but hey, add another access to another variable in the same cache line that is accessed through another spinlock (to get cacheline ping-pong and timing effects), and I suspect you can make it happen even with a simple example like the above.

The reason it can return 1 quite legally is that your new "spin\_unlock()" isnot serializing any more, so there is very little effective ordering between the two actions

b = a;spin\_unlock();

as they access completely different data (ie no data dependencies in sight). So what you could end up doing is equivalent to

CPU#1 CPU#2 b = a; /\* cache miss, we'll delay this.. \*/

spin\_unlock();

spin\_lock();

a = 1;

/\* cache miss satisfied, the "a" line is boun

b gets the value 1

for speculative reads and store-buffer forwarding." He explained

A Pentium is a in-order machine, without any of the interesting speculation wrt reads etc. So on a Pentium you'll never see the problem.

We can shave spin\_unlock() down from about 22 ticks for the "lock; btrl \$0,%0" asm code, to 1 tick for a simple "movl \$0,%0" instruction, a huge gain.

> kernels don't hit it (Netware 4/5 uses this method but it's spinlocks understand this and the code is writtne to handle it. The most obvious aberrant behavior was that cache inconsistencies would occur randomly. PPro uses lock to signal that the piplines are no longer invalid and the buffers should be blown out.

I have seen the behavior Linus describes on a hardware analyzer, BUT ONLY ON SYSTEMS THAT WERE PPRO AND ABOVE. I guess the BSD people must still be on older Pentium hardware and that's why they don't know this can bite in some cases.

Erich Boleyn, an Architect in an IA32 development group at Intel, also replied to Linus, pointing out a possible misconception in his proposed exploit. Regarding the code Linus posted, Erich replied:

It will always return 0. You don't need "spin\_unlock()" to be serializing.

The only thing you need is to make sure there is a store in "spin\_unlock()", and that is kind of true by the fact that you're changing something to be observable on other processors.

The reason for this is that stores can only possibly be observed when all prior instructions have retired (i.e. the store is not sent outside of the processor until it is committed state, and the earlier instructions are already committed by that time), so the any loads, stores, etc absolutely have to have completed first, cache-miss or not.

#### He went on:

Since the instructions for the store in the spin\_unlock have to have been externally observed for spin\_lock to be aquired (presuming a correctly functioning spinlock, of course), then the earlier instructions to set "b" to the value of "a" have to have completed first.

In general, IA32 is Processor Ordered for cacheable accesses. Speculation doesn't affect this. Also, stores are not observed speculatively on other processors.

There was a long clarification discussion, resulting in a complete turnaround by Linus:

Everybody has convinced me that yes, the Intel ordering rules \_are\_ strong enough that all of this really is legal, and that's what I wanted. I've gotten sane explanations for why serialization (as opposed to just the simple locked access) is required for the lock() side but not the unlock() side, and that lack of symmetry was what bothered me the most.

Oliver made a strong case that the lack of symmetry can be adequately explained by just simply the lack of symmetry wrt speculation of reads vs writes. I feel comfortable again.

Thanks, guys, we'll be that much faster due to this..

20Nov1999-7Dec1999 (143 posts) Archive Link: "<u>spin\_unlock optimization(i386)</u>" Topics: <u>BSD: FreeBSD, SMP</u> People: <u>Linus Torvalds Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ingo</u>

#### People: Linus Forvaids, Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ing <u>Monar</u> Monfred Spraul thought hold found a superior shows with a show to be a figure of the state of the s

Manfred Spraul thought he'd found a way to shave spin\_unlock() down from about 22 ticks for the "lock; btrl \$0,%0" asm code, to 1 tick for a simple "movl \$0,%0" instruction, a huge gain. Later, he reported that Ingo Molnar noticed a 4% speed-up in a benchmark test, making the optimization very valuable. Ingo also added that the same optimization cropped up in the FreeBSD mailing list a few days previously. But Linus Torvalds poured cold water on the whole thing, saying:

#### It does NOT WORK!

Let the FreBSD people use it, and let them get faster timings. They will crash, eventually.

The window may be small, but if you do this, then suddenly spinlocks aren't reliable any more.

The issue is not writes being issued in-order (although all the Intel CPU books warn you NOT to assume that in-order write behaviour - I bet it won't be the case in the long run).

The issue is that you \_have\_ to have a serializing instruction in order to make sure that the processor doesn't re-order things around the unlock.

For example, with a simple write, the CPU can legally delay a read that happened inside the critical region (maybe it missed a cache line), and get a stale value for any of the reads that \_should\_ have been serialized by the spinlock.

spin\_unlock();

spin\_lock();

a = 1;

/\* cache miss satisfied, the "a" line is boun

b gets the value 1

for speculative reads and store-butter forwarding." He explained

A Pentium is a in-order machine, without any of the interesting speculation wrt reads etc. So on a Pentium you'll never see the problem.

Note that I actually thought this was a legal optimization, and for a while I had this in the kernel. It crashed. In random ways.

Note that the fact that it does not crash now is quite possibly because of either

we have a lot less contention on our spinlocks these days. That might hide the problem, because the \_spinlock\_ will be fine (the cache coherency still means that the spinlock itself works fine - it's just that it no longer works reliably as an exclusion thing)

the window is probably very very small, and you have to be unlucky to hit it. Faster CPU's, different compilers, whatever.

I might be proven wrong, but I don't think I am.

Note that another thing is that yes, "btcl" may be the worst possible thing to use for this, and you might test whether a simpler "xor+xchgl" might be better - it's still serializing because it is locked, but it should be the normal 12 cycles that Intel always seems to waste on serializing instructions rather than 22 cycles.

Elsewhere, he gave a potential (though unlikely) exploit:

As a completely made-up example (which will probably never show the problem in real life, but is instructive as an example), imaging running the

spin\_lock()

a = 1;

mb();

a = 0;

mb();

b = a;

spin\_unlock();

return b;

Now, OBVIOUSLY the above always has to return 0, right? All accesses to "a" are inside the spinlock, and we always set it to zero before we read it into "b" and return it. So if we EVER returned anything else, the spinlock would obviously be completely broken, wouldn't you say?

And yes, the above CAN return 1 with the proposed optimization. I doubt you can make it do so in real life, but hey, add another access to another variable in the same cache line that is accessed through another spinlock (to get cacheline ping-pong and timing effects), and I suspect you can make it happen even with a simple example like the above.

The reason it can return 1 quite legally is that your new "spin\_unlock()" is not serializing any more, so there is very little effective ordering between the two actions

#### b = a;spin\_unlock();

as they access completely different data (ie no data dependencies in sight). So

, we'll delay this.. \*/

4% speed-up in a benchmark test,<br/>making the optimization very valuable.We can sh<br/>about 22 tThe same optimization cropped up in<br/>the FreeBSD mailing list.

### asm code, to 1 tick for a simple "movi \$0,%0" instruction, a huge gain.

kernels don't hit it (Netware 4/5 uses this method but it's spinlocks understand this and the code is writtne to handle it. The most obvious aberrant behavior was that cache inconsistencies would occur randomly. PPro uses lock to signal that the piplines are no longer invalid and the buffers should be blown out.

I have seen the behavior Linus describes on a hardware analyzer, BUT ONLY ON SYSTEMS THAT WERE PPRO AND ABOVE. I guess the BSD people must still be on older Pentium hardware and that's why they don't know this can bite in some cases.

Erich Boleyn, an Architect in an IA32 development group at Intel, also replied to Linus, pointing out a possible misconception in his proposed exploit. Regarding the code Linus posted, Erich replied:

It will always return 0. You don't need "spin\_unlock()" to be serializing.

The only thing you need is to make sure there is a store in "spin\_unlock()", and that is kind of true by the fact that you're changing something to be observable on other processors.

20Nov1999-7Dec1999 (143 posts) Archive Link: "spin\_unlock optimization(i386)" Topics: BSD: FreeBSD, SMP People: Linus Torvalds, Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ingo

Manfred Spraul thought he'd found a way to shave spin unlock() down from about 22 ticks for the "lock; btrl \$0,%0" asm code, to 1 tick for a simple "movl \$0,%0" instruction, a huge gain. Later, he reported that Ingo Molnar noticed a 4% speedup in a benchmark test, making the optimization very valuable. Ingo also added that the same optimization cropped up in the FreeBSD mailing list a few days previously. But Linus Torvalds poured cold water on the whole thing, saying:

#### It does NOT WORK!

Let the FreBSD people use it, and let them get faster timings. They will crash, eventually.

The window may be small, but if you do this, then suddenly spinlocks aren't reliable any more.

The issue is not writes being issued in-order (although all the Intel CPU books warn you NOT to assume that in-order write behaviour - I bet it won't be the case in the long run).

The issue is that you \_have\_ to have a serializing instruction in order to make sure that the processor doesn't re-order things around the unlock.

For example, with a simple write, the CPU can legally delay a read that happened inside the critical stale value for any of the re spinlock.

spin\_unlock();

spin\_lock();

a = 1; /\* cache miss satisfied, the

b gets the value 1

a = 0; and it r

Unlikely bug in a

Manfred Manual,

the Penti writes in around b (cache n CPU wo a Pentiu

manual. for speculative reads and st

A Pentium is a in-order ma wrt reads etc. So on a Pentiu Note that I actually thought this was a legal optimization, and for a while I had this in the kernel. It crashed. In random ways.

Note that the fact that it does not crash now is quite possibly because of either

#### we have a lot less contention on our spinlocks these days. That might hide the problem, because the \_spinlock\_ will be fine (the cache coherency still means that the spinlock itself works fine - it's just that it no longer works reliably as an exclusion thing)

the window is probably very very small, and you have to be unlucky to hit it. Faster CPU's, different compilers, whatever.

spin\_lock() mb(); a = 0; mb(); b = a;spin\_unlock(); return b;

Now, OBVIOUSLY the above always has to return 0, right? All accesses to "a" are inside the spinlock, and we always set it to zero before we read it into "b" and return it. So if we EVER returned anything else, the spinlock would obviously be completely broken, wouldn't you say?

**It does NOT WORK!** above. Let the FreBSD people use it, and let them get faster timings. They will crash, eventually. ay this.. \*/

g the optimization very valuable. ame optimization cropped up in the FreeBSD mailing list.

### ck for a simple "movi ction, a huge gain.

n't hit it (Netware 4/5 uses this method but it's spinlocks d this and the code is writtne to handle it. The most obvious behavior was that cache inconsistencies would occur randomly. lock to signal that the piplines are no longer invalid and the buffers blown out.

n the behavior Linus describes on a hardware analyzer, BUT N SYSTEMS THAT WERE PPRO AND ABOVE. I guess the BSD st still be on older Pentium hardware and that's why they don't can bite in some cases.

yn, an Architect in an IA32 development group at Intel, also replied to nting out a possible misconception in his proposed exploit. Regarding inus posted, Erich replied:

ays return 0. You don't need "spin\_unlock()" to be serializing.

hing you need is to make sure there is a store in "spin unlock()", s kind of true by the fact that you're changing something to be observable on other processors.

rn 1 with the proposed optimization. I doubt you but hey, add another access to another variable accessed through another spinlock (to get cachects), and I suspect you can make it happen even

ite legally is that your new "spin\_unlock()" isnot is very little effective ordering between the two

rent data (ie no data dependencies in sight). So equivalent to

s that stores can only possibly be observed when all prior tired (i.e. the store is not sent outside of the processor state, and the earlier instructions are already committed

20Nov1999-7Dec1999 (143 posts) Archive Link: "<u>spin\_unlock\_optimization(i386)</u>" Topics: <u>BSD: FreeBSD, SMP</u> People: <u>Linus Torvalds, Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ingo</u>

#### Propie: Linus Forvaids, Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ji <u>Molnar</u> Manfred Spraul thought hold from documents above and the bole for the bol

Manfred Spraul thought he'd found a way to shave spin\_unlock() down from about 22 ticks for the "lock; btrl \$0,%0" asm code, to 1 tick for a simple "movl \$0,%0" instruction, a huge gain. Later, he reported that Ingo Molnar noticed a 4% speed-up in a benchmark test, making the optimization very valuable. Ingo also added that the same optimization cropped up in the FreeBSD mailing list a few days previously. But Linus Torvalds poured cold water on the whole thing, saying:

### It does NOT WORK!

Let the FreBSD people use it, and let them get faster timings. They will crash, eventually.

The window may be small, but if you do this, then suddenly spinlocks aren't reliable any more.

The issue is not writes being issued in-order (although all the Intel CPU books warn you NOT to assume that in-order write behaviour - I bet it won't be the case in the long run).

The issue is that you \_have\_ to have a serializing instruction in sure that the processor doesn't re-order things around the unlo

For example, with a simple write, the CPU can legally delay a r happened inside the critical stale value for any of the re spinlock.

spin\_unlock();

Note that I actually thought this was a legal optimization, and for a while I had this in the kernel. It crashed. In random ways.

Note that the fact that it does not crash now is quite possibly because of either

we have a lot less contention on our spinlocks these days. That might hide the problem, because the \_spinlock\_ will be fine (the cache coherency still means that the spinlock itself works fine - it's just that it no longer works reliably as an exclusion thing)

the window is probably very very small, and you have to be unlucky to hit it. Faster CPU's, different compilers, whatever.

DOD

spin\_lock()

a = 1;

mb();

a = 0;

mb();

b = a;

spin\_unlock();

return b;

Now, OBVIOUSLY the above always has to return 0, right? All accesses to "a" are inside the spinlock, and we always set it to zero before we read it into "b" and return it. So if we EVER returned anything else, the spinlock would obviously be completely broken, wouldn't you say?

s very little effective ordering between the two

**It does NOT WORK!** It elegally is that your new "spin\_unlock()" isnot

According to the *Pentium Processor Family Developers Manual, Vol3, Chapter 19.2 Memory Access Ordering*, "to optimize performance, the Pentium processor allows memory reads to be reordered ahead of buffered writes in most situations. Internally, CPU reads (cache hits) can be reordered around buffered writes. Memory reordering does not occur at the pins, reads (cache miss) and writes appear in-order."

> on't hit it (Netware 4/5 uses this method but it's spinlocks d this and the code is writtne to handle it. The most obvious behavior was that cache inconsistencies would occur randomly. lock to signal that the piplines are no longer invalid and the buffers blown out.

n the behavior Linus describes on a hardware analyzer, BUT SYSTEMS THAT WERE PPRO AND ABOVE. I guess the BSD ist still be on older Pentium hardware and that's why they don't can bite in some cases.

yn, an Architect in an IA32 development group at Intel, also replied to nting out a possible misconception in his proposed exploit. Regarding inus posted, Erich replied:

ays return 0. You don't need "spin\_unlock()" to be serializing.

Ouest-France

hing you need is to make sure there is a store in "spin\_unlock()", s kind of true by the fact that you're changing something to be observable on other processors.

for speculative reads and sto

A Pentium is a in-order ma

wrt reads etc. So on a Pentiu

20Nov1999-7Dec1999 (143 posts) Archive Link: "<u>spin\_unlock optimization(i386)</u>" Topics: <u>BSD: FreeBSD, SMP</u> People: <u>Linus Torvalds Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ingo</u>

#### People: Linus Torvalds, Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, In <u>Molnar</u> Mar feed Science Management Andre Science and Sci

Manfred Spraul thought he'd found a way to shave spin\_unlock() down from about 22 ticks for the "lock; btrl \$0,%0" asm code, to 1 tick for a simple "movl \$0,%0" instruction, a huge gain. Later, he reported that Ingo Molnar noticed a 4% speed-up in a benchmark test, making the optimization very valuable. Ingo also added that the same optimization cropped up in the FreeBSD mailing list a few days previously. But Linus Torvalds poured cold water on the whole thing, saying:

### It does NOT WORK!

Let the FreBSD people use it, and let them get faster timings. They will crash, eventually.

The window may be small, but if you do this, then suddenly spinlocks aren't reliable any more.

The issue is not writes being warn you NOT to assume case in the long run).

The issue is that you \_have sure that the processor do

For example, with a simple happened inside the critica stale value for any of the r spinlock.

spin\_unlock();

From the Pentium Pro manual, "The only enhancement in the PentiumPro processor is the added support for speculative reads and store-buffer forwarding."

an exclusion thing)

around buffered writes. Memory re the pins, reads (cache miss) and

Note that I actually thought this was a legal optimization, and for a while I

Note that the fact that it does not crash now is quite possibly because of either

we have a lot less contention on our spinlocks these days. That might hide the

problem, because the \_spinlock\_ will be fine (the cache coherency still means

that the spinlock itself works fine - it's just that it no longer works reliably as

the window is probably very very small, and you have to be unlucky to hit it.

**It does NOT WORK!**

had this in the kernel. It crashed. In random ways.

Faster CPU's, different compilers, whatever.

on't hit it (Netware 4/5 uses this method but it's spinlocks of this and the code is writtne to handle it. The most obvious behavior was that cache inconsistencies would occur randomly. lock to signal that the piplines are no longer invalid and the buffers blown out.

n the behavior Linus describes on a hardware analyzer, BUT N SYSTEMS THAT WERE PPRO AND ABOVE. I guess the BSD ist still be on older Pentium hardware and that's why they don't can bite in some cases.

yn, an Architect in an IA32 development group at Intel, also replied to nting out a possible misconception in his proposed exploit. Regarding inus posted, Erich replied:

ays return 0. You don't need "spin\_unlock()" to be serializing.

hing you need is to make sure there is a store in "spin\_unlock()", s kind of true by the fact that you're changing something to be observable on other processors. spin\_lock()

a = 1;

mb();

a = 0;

mb();

b = a;

spin\_unlock();

return b;

Now, OBVIOUSLY the above always has to return 0, right? All accesses to "a" are inside the spinlock, and we always set it to zero before we read it into "b" and return it. So if we EVER returned anything else, the spinlock would obviously be completely broken, wouldn't you say?

ory Accoss Ordering "to

I'm 1 with the proposed optimization. I doubt you but hey, add another access to another variable accessed through another spinlock (to get cacheects), and I suspect you can make it happen even e above.

ite legally is that your new "spin\_unlock()" isnot is very little effective ordering between the two

'V

" to the

ation

ind by

strong otten

locked

for speculative reads and sto

A Pentium is a in-order ma wrt reads etc. So on a Pentium you n hever see

20Nov1999-7Dec1999 (143 posts) Archive Link: "spin\_unlock optimization(i386)" Topics: BSD: FreeBSD, SMP People: Linus Torvalds, Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ingo

Manfred Spraul thought he'd found a way to shave spin unlock() down from about 22 ticks for the "lock; btrl \$0,%0" asm code, to 1 tick for a simple "movl \$0,%0" instruction, a huge gain. Later, he reported that Ingo Molnar noticed a 4% speedup in a benchmark test, making the optimization very valuable. Ingo also added that the same optimization cropped up in the FreeBSD mailing list a few days previously. But Linus Torvalds poured cold water on the whole thing, saying:

### It does NOT WORK!

Let the FreBSD people use it, and let them get faster timings. They will crash, eventually.

The window may be small, but if you do this, then suddenly spinlocks aren't reliable any more.

The issue is not writes being warn you NOT to assume case in the long run).

The issue is that you \_have sure that the processor do

For example, with a simpl happened inside the critic stale value for any of the spinlock.

Note that I actually thought this was a legal optimization, and for a while I had this in the kernel. It crashed. In random ways.

Note that the fact that it does not crash now is quite possibly because of either

we have a lot less contention on our spinlocks these days. That might hide the problem, because the \_spinlock\_ will be fine (the cache coherency still means that the spinlock itself works fine - it's just that it no longer works reliably as an exclusion thing)

spin\_lock() mb(); a = 0; mb(); b = a;spin\_unlock(); return b;

Now, OBVIOUSLY the above always has to return 0, right? All accesses to "a" are inside the spinlock, and we always set it to zero before we read it into e, the spinlock would

I have seen the behavior Linus describes on a hardware analyzer, BUT ONLY ON From the Pe SYSTEMS THAT WERE PPRO AND only enhanc **ABOVE.** I guess the BSD people must still be processor i on older Pentium hardware and that's why speculative they don't know this can bite in some cases.

"spin\_unlock()" isnot ing between the two

Y

' to the

tion

ind by

strong otten

locked

S

'ta

### writes. Memory re (cache miss) and

are 4/5 uses this method but it's spinlocks ode is writtne to handle it. The most obvious at cache inconsistencies would occur randomly. hat the piplines are no longer invalid and the buffers

Linus describes on a hardware analyzer, BUT HAT WERE PPRO AND ABOVE. I guess the BSD der Pentium hardware and that's why they don't e cases.

in an IA32 development group at Intel, also replied to ble misconception in his proposed exploit. Regarding inus posted, Erich replied:

ays return 0. You don't need "spin\_unlock()" to be serializing.

**Ouest-France**

hing you need is to make sure there is a store in "spin unlock()", s kind of true by the fact that you're changing something to be observable on other processors.

for speculative reads and sto

A Pentium is a in-order ma

wrt reads etc. So on a Pentio

20Nov1999-7Dec1999 (143 posts) Archive Link: "<u>spin\_unlock\_optimization(i386)</u>" Topics: <u>BSD: FreeBSD, SMP</u> People: <u>Linus Torvalds, Jeff V. Merkey, Erich Bolevn, Manfred Spraul, Peter Samuelson, Ingo</u>

People: <u>Linus Torvalds, Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ingo</u> <u>Molnar</u> Manfred Spraul thought he'd found a way to shave spin\_unlock() down from about

Manfred Sprall thought he d found a way to shave spin\_unlock() down from about 22 ticks for the "lock; btrl \$0,%0" asm code, to 1 tick for a simple "movl \$0,%0" instruction, a huge gain. Later, he reported that Ingo Molnar noticed a 4% speedup in a benchmark test, making the optimization very valuable. Ingo also added that the same optimization cropped up in the FreeBSD mailing list a few days previously. But Linus Torvalds poured cold water on the whole thing, saying: Note that I actually thought this was a legal optimization, and for a while I had this in the kernel. It crashed. In random ways.

Note that the fact that it does not crash now is quite possibly because of either

we have a lot less contention on our spinlocks these days. That might hide the problem, because the \_spinlock\_ will be fine (the cache coherency still means that the spinlock itself works fine - it's just that it no longer works reliably as an exclusion thing)

spin\_lock()

a = 1;

mb();

a = 0;

mb();

b = a;

spin\_unlock();

return b;

Now, OBVIOUSLY the above always has to return 0, right? All accesses to "a" are inside the spinlock, and we always set it to zero before we read it into

20Nov1999-7Dec1999 (143 posts) Archive Link: "<u>spin\_unlock\_optimization(i386)</u>" Topics: <u>BSD: FreeBSD, SMP</u> People: <u>Linus Torvalds Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ingo</u>

People: <u>Linus Torvalds, Jeff V. Merkey, Erich Boleyn, Manfred Spraul, Peter Samuelson, Ing</u> <u>Molnar</u> Marfred Samuel dans to be the formula manufactor of the second sec

Manfred Spraul thought he'd found a way to shave spin\_unlock() down from about 22 ticks for the "lock; btrl \$0,%0" asm code, to 1 tick for a simple "movl \$0,%0" instruction, a huge gain. Later, he reported that Ingo Molnar noticed a 4% speed-up in a benchmark test, making the optimization very valuable. Ingo also added that the same optimization cropped up in the FreeBSD mailing list a few days previously. But Linus Torvalds poured cold water on the whole thing, saying:

Note that I actually thought this was a legal optimization, and for a while I had this in the kernel. It crashed. In random ways.

Note that the fact that it does not crash now is quite possibly because of either

we have a lot less contention on our spinlocks these days. That might hide the problem, because the \_spinlock\_ will be fine (the cache coherency still means that the spinlock itself works fine - it's just that it no longer works reliably as an exclusion thing)

spin\_lock()

a = 1;

mb();

a = 0;

mb();

b = a;

spin\_unlock();

return b;

Now, OBVIOUSLY the above always has to return 0, right? All accesses to "a" are inside the spinlock, and we always set it to zero before we read it into

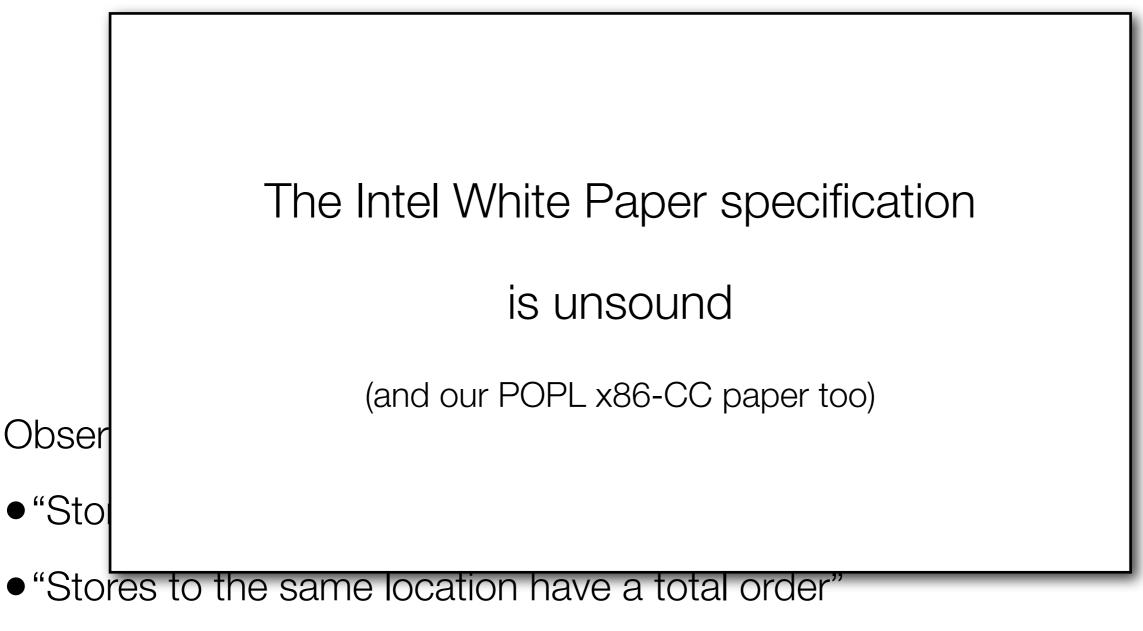

# Intel 64/IA32 and AMD64 - Aug. 2007 / Oct. 2008

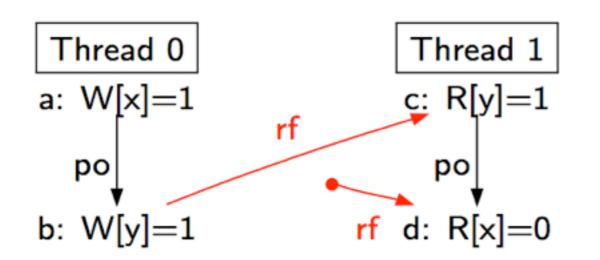

Intel publishes a white paper, defining 8 informal-prose principles, e.g.

P1. Loads are not reordered with older loads.

P2. Stores are not reordered with older stores.

supported by 10 litmus test (illustrating allowed or forbidden behaviours), e.g.:

| Thread 0                                       | Thread 1                     |  |  |

|------------------------------------------------|------------------------------|--|--|

| MOV [x] ← 1                                    | MOV EAX $\leftarrow$ [y] (1) |  |  |

| MOV [y] ← 1                                    | MOV EBX ← [x] (0)            |  |  |

| Forbidden final state: EAX = $1 \land EBX = 0$ |                              |  |  |

P3. Loads may be reordered with older stores to different locations but not with older stores to the same location.

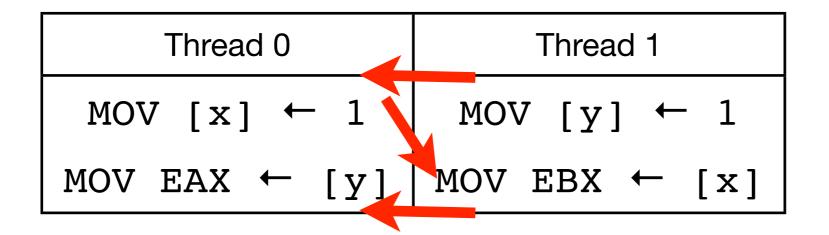

| Thread 0                         | Thread 1           |

|----------------------------------|--------------------|

| MOV [x] ← 1                      | MOV [y] ← 1        |

| MOV EAX $\leftarrow$ [y] (0)     | MOV EBX ← [x] (0)  |

| Allowed final state: $0:EAX = 0$ | $\wedge 1:EBX = 0$ |

P3. Loads may be reordered with older stores to different locations but not with older stores to the same location.

| Thread 0                         | Thread 1                     |

|----------------------------------|------------------------------|

| MOV [x] ← 1                      | MOV [y] ← 1                  |

| MOV EAX $\leftarrow$ [y] (0)     | MOV EBX $\leftarrow$ [x] (0) |

| Allowed final state: $0:EAX = 0$ | $\wedge 1:EBX = 0$           |

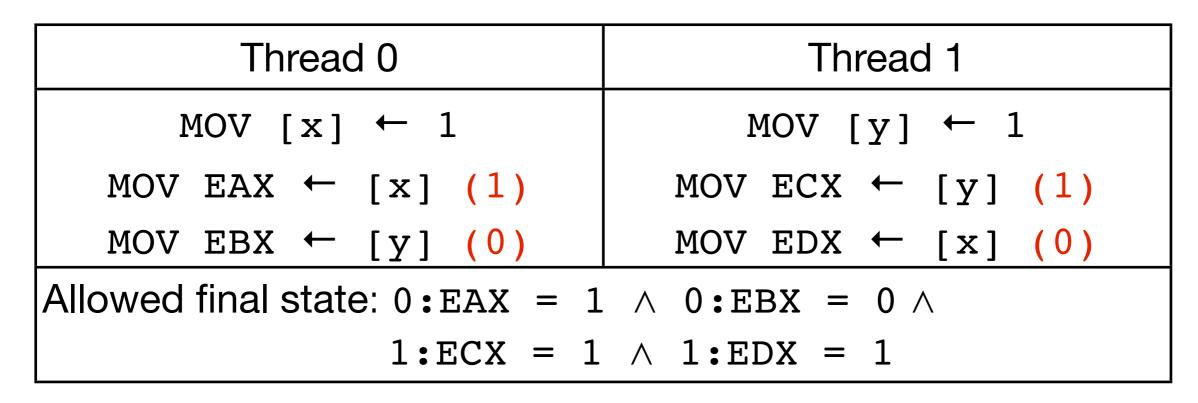

### Litmus test 2.4: intra-processor forwarding is allowed

| Thread 0                         | Thread 1                     |

|----------------------------------|------------------------------|

| MOV [x] ← 1                      | MOV [y] ← 1                  |

| MOV EAX $\leftarrow$ [x] (1)     | MOV ECX $\leftarrow$ [y] (1) |

| MOV EBX $\leftarrow$ [y] (0)     | MOV EDX $\leftarrow$ [x] (0) |

| Allowed final state: $0:EAX = 1$ | $\wedge$ 0:EBX = 0 $\wedge$  |

| 1:ECX = 1                        | $\wedge$ 1:EDX = 1           |

### Litmus test 2.4: intra-processor forwarding is allowed

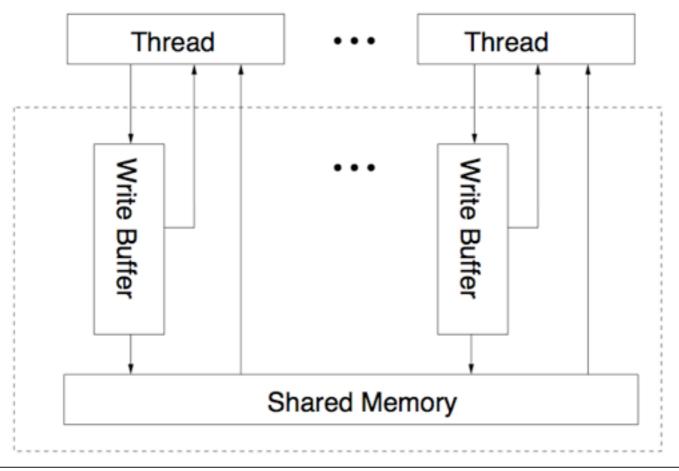

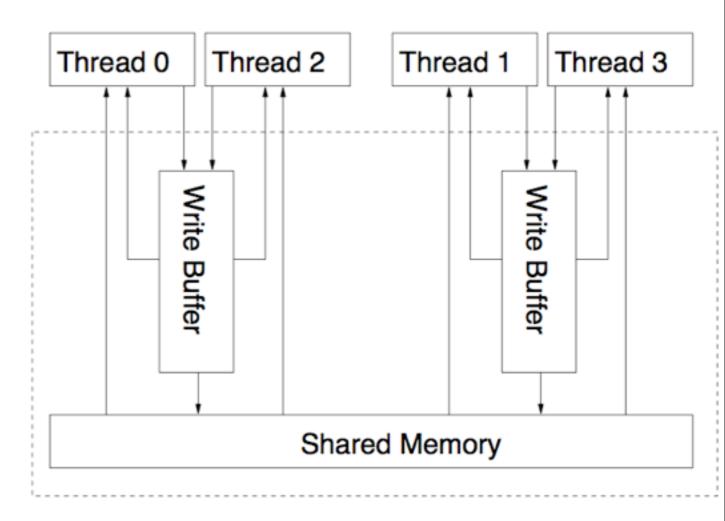

| -                                                                            | Thread | 0 |   | -   | Thread |   | Thread 2 |     |     |   |           | Threa    | d 3 |   |            |

|------------------------------------------------------------------------------|--------|---|---|-----|--------|---|----------|-----|-----|---|-----------|----------|-----|---|------------|

| MOV                                                                          | [X]    | ← | 1 | MOV | [y]    | ← | 1        | MOV | EAX | ← | [x]<br>(1 | MOV<br>) | ECX | ← | [y]<br>(1) |

|                                                                              |        |   |   |     |        |   |          | MOV | EBX | ← | [y]<br>(0 | MOV<br>) | EDX | ← | [x]<br>(0) |

| Final state: 2:EAX = 1 $\land$ 2:EBX = 0 $\land$ 3:ECX = 1 $\land$ 3:EDX = 0 |        |   |   |     |        |   |          |     |     |   |           |          |     |   |            |

| -     | Thread | 0    |    | -    | Thread | 1  |    | Thread 2 |        |    |           |          | Threa | d 3 |            |

|-------|--------|------|----|------|--------|----|----|----------|--------|----|-----------|----------|-------|-----|------------|

| MOV   | [X]    | ←    | 1  | MOV  | [y]    | ←  | 1  | MOV      | EAX    | ←  | [x]<br>(1 | MOV<br>) | ECX   | ←   | [y]<br>(1) |

|       |        |      |    |      |        |    |    | MOV      | EBX    | ←  | [y]<br>(0 | MOV<br>) | EDX   | ←   | [x]<br>(0) |

| Final | state  | : 2: | EA | AX = | 1 ^    | 2: | EB | x = C    | ) ^ 3: | EC | x = 1     | . ^ 3    | EDX:  | =   | 0          |

Microarchitecturally plausible?

Yes, with e.g. shared store buffers.

P1-P4: ... may be reordered with ...

P5: Intel 64 memory ordering ensures transitive visibility of stores — i.e. stores that are causally related appear to execute in an order consistent with the causal relation.

| Thread 0            | Thread 1                     | Thread 2                     |  |  |  |  |

|---------------------|------------------------------|------------------------------|--|--|--|--|

| MOV [x] ← 1         | MOV EAX $\leftarrow$ [x] (1) | MOV EBX $\leftarrow$ [y] (1) |  |  |  |  |

|                     | MOV [y] ← 1                  | MOV ECX $\leftarrow$ [x] (0) |  |  |  |  |

| Forbidden final sta | ate: 1:EAX = $1 \land 2:EBX$ | $X = 1 \wedge 2:ECX = 0$     |  |  |  |  |

# Ambiguity

P1-P4: ... may be reordered with ...