## THÈSE DE DOCTORAT

de l'Université de recherche Paris Sciences Lettres PSL Research University

## Préparée à l'École normale supérieure

# **Compiler Optimisations and Relaxed Memory Consistency Models**

ED 386 SCIENCES MATHÉMATIQUES DE PARIS CENTRE Spécialité INFORMATIQUE

## Robin Morisset

Version du 12/07/2017

Dirigée par Francesco Zappa Nardelli

#### COMPOSITION DU JURY:

M. Andrew Appel

Princeton University

Rapporteur (non membre du jury)

M. Doug Lea State University of New York Rapporteur

M. Mark Batty

University of Kent

Examinateur

M. Derek Dreyer Max Planck Institute for Software Systems Examinateur

M. Marc Pouzet École normale supérieure Président du jury

M. Dmitry Vyukov Google Examinateur

M. Francesco Zappa Nardelli Inria Directeur de thèse

## Acknowledgments

First, I would like to thank Francesco for being the best advisor I could have hoped for, leaving me great freedom in what to research while always being available when I needed advice. I hope to have learned some of his riguor and pedagogy through these years.

I am also grateful to all the members of my jury for their participation, and in particular to Andrew and Doug for having reviewed very thoroughly this thesis in such a short time.

I was supported throughout this work by a fellowship from Google for which I am thankful. Google, and J.F. Bastien in particular also offered me the wonderful opportunity to apply my research in the Clang compiler through a 3 month internship that I greatly appreciated.

Throughout the rest of my thesis I frequently interacted with the other members of the Parkas team, who made it a very welcoming place to work. I would especially like to thank Guillaume Baudart, Adrien Guatto and Nhat Minh Lê for the many coffee breaks we shared discussing everything and anything, and for the sleepless nights I spent writing papers with Adrien and Nhat.

Obviously, research is frequently a group effort, and I would like to thank now all those I collaborated with over the past few years. Obviously this includes Francesco, Adrien, and Nhat, but also Thibaut Balabonski, Pankaj Pawan, and Viktor Vafeiadis. I also benefited from more informal research collaborations and discussions, in particular with Peter Sewell's team in Cambridge: Mark Batty, Kayvan Memarian, Jean Pichon, Peter Sewell and others made each of my trips to Cambridge remarkably productive and enjoyable.

I am also deeply thankful to Jean-Christophe Filliâtre. He not only made me discover research on compilers through his course in 2009 and his recommendation for my first internship; he also made me a TA in 2015 for his compilation course. This teaching work was a pleasure, with wonderful students, and gave me something to look forward to every week, even when nothing was working on the research side.

I would also like to thank my family, for believing in me even when I didn't and supporting me all these years. I wouldn't be here without you.

Last but not least, I would like to thank all of my friends, who made these years bearable and often even fun.

## Contents

| 1        | Why study compiler optimisations of shared memory programs? |                                           |                                                    |    |  |  |  |  |

|----------|-------------------------------------------------------------|-------------------------------------------|----------------------------------------------------|----|--|--|--|--|

| <b>2</b> | Ар                                                          | rimer                                     | on memory models                                   | 9  |  |  |  |  |

|          | 2.1                                                         | Exam                                      | ples of non-sequentially consistent behaviors      | 9  |  |  |  |  |

|          | 2.2                                                         | Hardw                                     | vare memory models                                 | 10 |  |  |  |  |

|          |                                                             | 2.2.1                                     | The x86 architecture                               | 10 |  |  |  |  |

|          |                                                             | 2.2.2                                     | The Power and ARM architectures                    | 13 |  |  |  |  |

|          |                                                             | 2.2.3                                     | Other architectures                                | 17 |  |  |  |  |

|          | 2.3 Language memory models                                  |                                           |                                                    |    |  |  |  |  |

|          |                                                             | 2.3.1                                     | Compiler optimisations in the Power model?         | 18 |  |  |  |  |

|          |                                                             | 2.3.2                                     | Data-Race Freedom (DRF)                            | 20 |  |  |  |  |

|          |                                                             | 2.3.3                                     | The C11/C++11 model $\dots$                        | 20 |  |  |  |  |

| 3        | Issues with the C11 model and possible improvements         |                                           |                                                    |    |  |  |  |  |

|          |                                                             | 3.0.1                                     | Consume accesses                                   | 28 |  |  |  |  |

|          |                                                             | 3.0.2                                     | SC fences                                          | 29 |  |  |  |  |

|          | 3.1                                                         | Sanity                                    | properties                                         | 29 |  |  |  |  |

|          |                                                             | 3.1.1                                     | Weakness of the SCReads axiom                      | 29 |  |  |  |  |

|          |                                                             | 3.1.2                                     | Relaxed atomics allow causality cycles             | 30 |  |  |  |  |

|          | 3.2                                                         | Furthe                                    | er simplifications and strengthenings of the model | 34 |  |  |  |  |

|          |                                                             | 3.2.1                                     | Simplifying the coherency axioms                   | 34 |  |  |  |  |

|          |                                                             | 3.2.2                                     | The definition of release sequences                | 36 |  |  |  |  |

|          |                                                             | 3.2.3                                     | Intra-thread synchronisation is needlessly banned  | 36 |  |  |  |  |

| 4        | Cor                                                         | Correct optimizations in the C11 model 38 |                                                    |    |  |  |  |  |

|          | 4.1                                                         | Optim                                     | ising accesses around atomics                      | 39 |  |  |  |  |

|          |                                                             | 4.1.1                                     | Eliminations of actions                            | 39 |  |  |  |  |

|          |                                                             | 4.1.2                                     | Reorderings of actions                             | 43 |  |  |  |  |

|          |                                                             | 4.1.3                                     | Introductions of actions                           | 44 |  |  |  |  |

|          | 4.2                                                         | Optim                                     | nizing atomic accesses                             | 44 |  |  |  |  |

|          |                                                             | 4.2.1                                     | Basic Metatheory of the Corrected C11 Models       |    |  |  |  |  |

|          |                                                             | 4.2.2                                     | Verifying Instruction Reorderings                  | 47 |  |  |  |  |

|          |                                                             | 4.2.3                                     | Counter-examples for unsound reorderings           | 50 |  |  |  |  |

|          |                                                             | 4.2.4                                     | Verifying Instruction Eliminations                 | 57 |  |  |  |  |

| 5        | Fuzzy-testing GCC and Clang for compiler concurrency bugs 6 |                                           |                                                    |    |  |  |  |  |

|          | 5.1                                                         | Comp                                      | iler concurrency bugs                              | 61 |  |  |  |  |

|          | 5.2                                                         | _                                         | iler Testing                                       | 64 |  |  |  |  |

|          | 5.3                                                         |                                           | t on compiler development                          | 69 |  |  |  |  |

| 6 | Lib                                                     | KPN: A                                       | A scheduler for Kahn Process Networks using C11 atomics | 72   |  |  |  |  |

|---|---------------------------------------------------------|----------------------------------------------|---------------------------------------------------------|------|--|--|--|--|

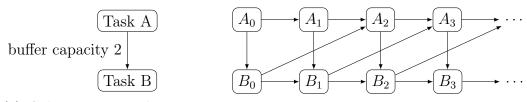

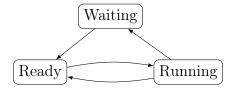

|   | 6.1                                                     | Schedu                                       | ıling of Kahn Process Networks                          | . 72 |  |  |  |  |

|   |                                                         | 6.1.1                                        | Graphs of dependencies between task activations         | . 73 |  |  |  |  |

|   |                                                         | 6.1.2                                        | Scheduling: why naive approaches fail                   | . 73 |  |  |  |  |

|   | 6.2                                                     | Algorit                                      | thms for passive waiting                                | . 75 |  |  |  |  |

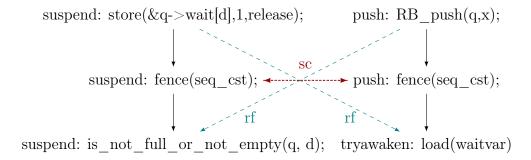

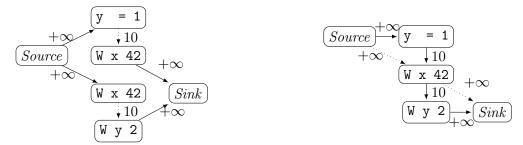

|   |                                                         | 6.2.1                                        | Algorithm F: double-checking in suspend                 | . 75 |  |  |  |  |

|   |                                                         | 6.2.2                                        | Algorithm S: removing fences on the critical path       | . 78 |  |  |  |  |

|   |                                                         | 6.2.3                                        | Algorithm H: keeping the best of algorithms F and S     | . 78 |  |  |  |  |

|   |                                                         | 6.2.4                                        | Going beyond KPNs: adding select in algorithm H         | . 79 |  |  |  |  |

|   |                                                         | 6.2.5                                        | Implementation details                                  | 81   |  |  |  |  |

|   | 6.3                                                     | Proofs                                       | of correctness                                          | . 85 |  |  |  |  |

|   |                                                         | 6.3.1                                        | Outline of the difficulties and methods                 | . 85 |  |  |  |  |

|   |                                                         | 6.3.2                                        | Absence of races                                        | . 86 |  |  |  |  |

|   |                                                         | 6.3.3                                        | Guarantee of progress                                   | 90   |  |  |  |  |

|   | 6.4                                                     | Remark                                       | ks on C11 programming                                   | . 93 |  |  |  |  |

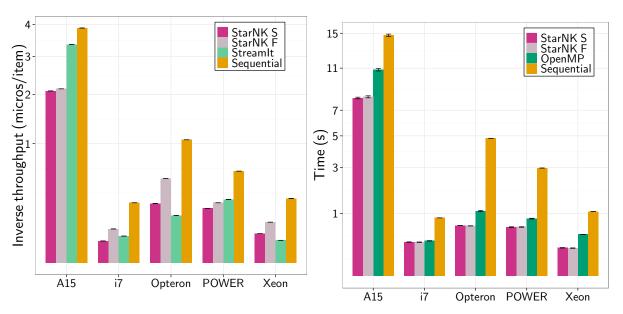

|   | 6.5                                                     | Applica                                      | ations and experimental evaluation                      | 94   |  |  |  |  |

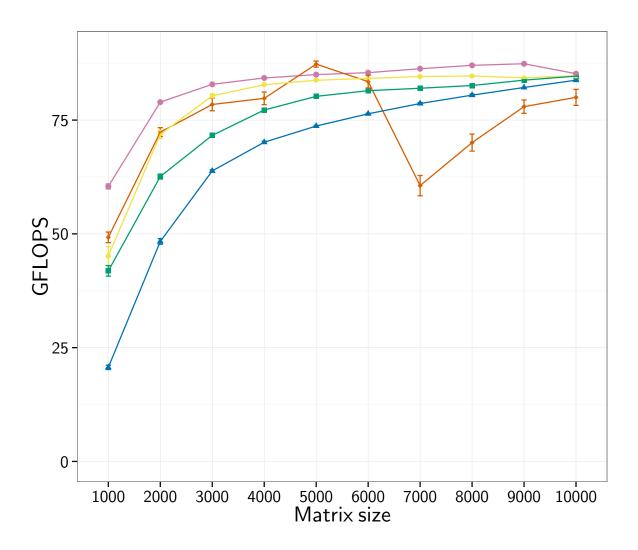

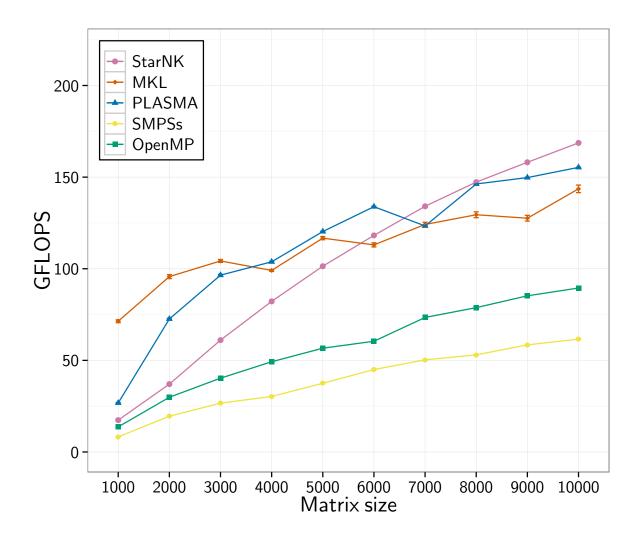

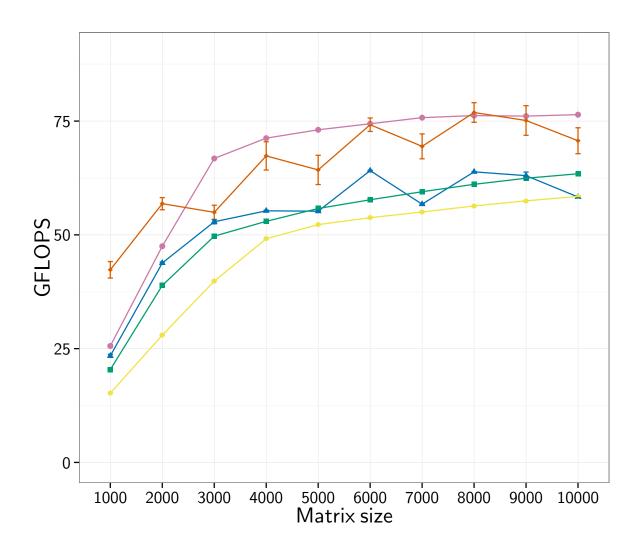

|   |                                                         | 6.5.1                                        | Micro-benchmarks                                        |      |  |  |  |  |

|   |                                                         | 6.5.2                                        | Dataflow benchmarks                                     |      |  |  |  |  |

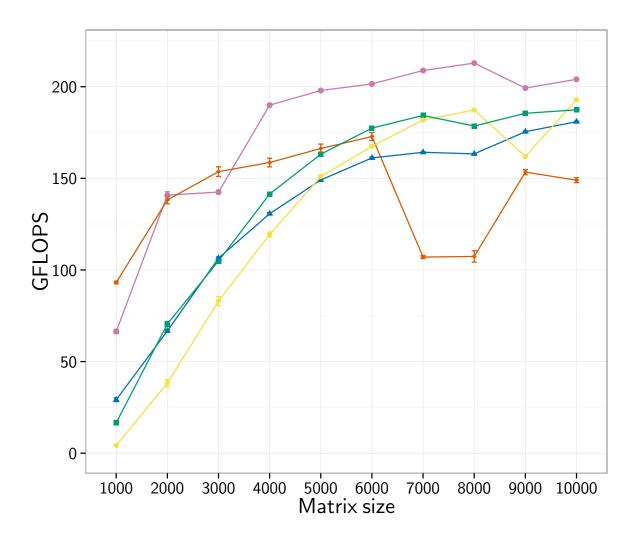

|   |                                                         | 6.5.3                                        | Linear algebra benchmarks                               | . 97 |  |  |  |  |

| 7 | A fence elimination algorithm for compiler backends 103 |                                              |                                                         |      |  |  |  |  |

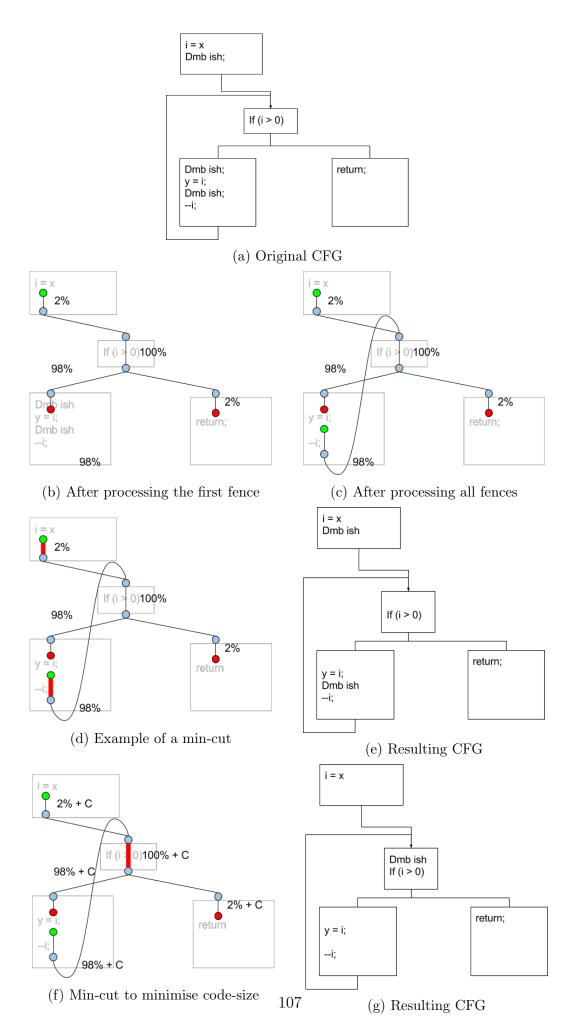

| • | 7.1                                                     |                                              | E-inspired fence elimination algorithm                  |      |  |  |  |  |

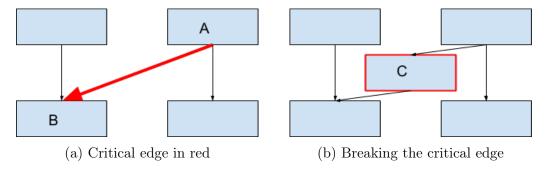

|   |                                                         | 7.1.1                                        | Leveraging PRE                                          |      |  |  |  |  |

|   |                                                         | 7.1.2                                        | The algorithm on a running example                      |      |  |  |  |  |

|   |                                                         | 7.1.3                                        | Corner cases                                            |      |  |  |  |  |

|   |                                                         | 7.1.4                                        | Proof of correctness                                    |      |  |  |  |  |

|   | 7.2                                                     |                                              | nentation and extensions to other ISAs                  |      |  |  |  |  |

|   | 7.3                                                     | <del>-</del>                                 |                                                         |      |  |  |  |  |

| o | D.,,                                                    | <b>4:</b>                                    |                                                         | 115  |  |  |  |  |

| 8 |                                                         | $\frac{\mathbf{spectiv}}{\mathbf{Polestor}}$ | es<br>d work                                            |      |  |  |  |  |

|   | 0.1                                                     |                                              | About optimisations in a concurrent context             |      |  |  |  |  |

|   |                                                         | 8.1.2                                        | About fuzzy-testing of compilers                        |      |  |  |  |  |

|   |                                                         | 8.1.3                                        | About LibKPN                                            |      |  |  |  |  |

|   |                                                         | 8.1.4                                        | About fence elimination                                 |      |  |  |  |  |

|   | 8.2                                                     | -                                            | work                                                    |      |  |  |  |  |

|   | 0.4                                                     | 8.2.1                                        | About the C11 model                                     |      |  |  |  |  |

|   |                                                         | 8.2.2                                        | About the fence elimination algorithm                   |      |  |  |  |  |

|   |                                                         | 8.2.3                                        | About LibKPN                                            |      |  |  |  |  |

| ٨ | Dno                                                     | of of T                                      | heorem 4                                                | 131  |  |  |  |  |

|   |                                                         |                                              | HEULEH +                                                |      |  |  |  |  |

## Chapter 1

# Why study compiler optimisations of shared memory programs?

Multicore computers have become ubiquitous, in servers, personal computers and even phones. The lowest abstraction for programming them is the *shared-memory*, *multi-threaded program*, in which several sequences of instructions (threads) are executed concurrently, accessing the same data. When these programs are compiled, it is usually done piecemeal: the compiler only see fragments of a thread at any time, unaware of the existence of other threads. This disconnect can lead compilers to break the expectations of the programmers regarding such multi-threaded programs. Consider for example the following program which shows two threads executing side-by-side:

| Initially, $x = y = 0$ |                |  |  |  |

|------------------------|----------------|--|--|--|

| Thread 1               | Thread 2       |  |  |  |

| x := 1;                | if $(x > 0)$ { |  |  |  |

| if $(y > 0)$ {         | x := 0;        |  |  |  |

| <pre>print x;</pre>    | y := 1;        |  |  |  |

| }                      | }              |  |  |  |

It has two global variables, x and y which are initialized at 0, and they are shared by the two threads. We assume both threads are started at the same time. What values can the first thread print? At first glance, 0 is the only value that can be printed: if the conditional in the left thread is taken, it means the store of 1 to y has happened, and so the store of 0 to x has happened too. Since it is also in a conditional, it must have happened after the store of 1 to x. So the value of x is 0 when it is printed.

But if the first thread is compiled by an optimising compiler, the compiler will execute the constant propagation optimisation: since there is no visible access to x between its store and its load, the compiler will assume the value has not changed and will replace print x by print 1, introducing a new behaviour.

Is this a bug in the compiler? No, the problem was our assumption that all threads have the same view of memory at all times, and that executing a multi-threaded program is equivalent to repeatedly picking one thread and executing it for one step. These assumptions are called the *Sequential Consistency model* (SC) and were first formalized in [Lam79]. Constant propagation is not the only optimisation that can break the SC model. Common Sub-expression Elimination (CSE), Loop Invariant Code Motion (LICM), Global Value Numbering (GVN) and Partial Redundancy Elimination (PRE)

are some other examples. Consequently, most languages have decided to offer weaker guarantees to the programmer, to preserve the compilers ability to perform these optimisations.

Even if a compiler were to forsake all SC-breaking optimisations, programmers still could not rely on the SC model, because of details in the architecture of the underlying processor. Consider for example the so-called *Store Buffering* pattern in Figure 1.1, where one thread writes to a variable and reads from another one, and another thread writes to the second variable and reads from the first one.

Figure 1.1: Store Buffering (SB) pattern

In an SC world, the outcomes of such a program can be listed by enumerating all possible interleavings of the threads (a more efficient way will be described later in the section on axiomatic memory models, see Section 2.2.2). Such an enumeration can easily prove that in any execution, at least one of the two print operations will print 1.

Yet, when implemented directly in assembly, this program will occasionally print two 0s on most multicore/multiprocessor platforms (including x86, ARM, Power, Sparc, Alpha). This can be explained by the presence of store buffers in these processors, so that they do not have to wait for stores to go all the way to memory. Loads check the local store buffer for stores to the same address so single-threaded programs do not notice this optimization, but it is observable to multi-threaded programs. In this instance for example, both stores can go into the store buffers, then both loads will check their own store buffer, not see any store to the same address, and load the value 0 from their cache (or directly from main memory). Only then will the stores be propagated to the memory. In practice, processors do not need to have physical store buffers to exhibit this behaviour, it can emerge from the coherency protocol of normal caches. In order to enforce the SC behaviour, it is necessary to include a special instruction between the stores and the loads, such as mfence on x86. All such instructions whose only purpose is to limit the observable effect of processor optimisations are called fences, and are usually quite slow.

As a consequence, programming languages that allow writing multi-threaded programs must carefully define what guarantees they offer the programmer. The compiler will then be able to both limit its optimisations and insert fence instructions in the right places to enforce these guarantees. Such a set of guarantees offered to the programmer by a platform is called a *memory model* (occasionally "memory consistency model" in the literature). The C and C++ standards committees have added such a memory model to these languages in 2011 (that we call the C11 model in the rest of this thesis). The C11 model is based on two ideas:

- 1. The compiler will ensure that code where no memory location is accessed concurrently behaves like in the SC model.

- 2. Otherwise, the programmer must add annotations to the loads and stores to describe what semantics they want from them. These annotated loads and stores are called *atomic operations* or just atomics, and the annotation is called a memory order

or attribute. Obviously, the stronger the semantics wanted, the more careful the compiler must be.

This model is convenient in that compilers can optimise code without concurrency primitives like in the SC model. They only have to be careful when encountering either locks or atomic operations: these force them to disable some of their own optimisations, and to introduce fence instructions to block processor optimisations.

Contributions In this thesis we present work on the optimisation of shared-memory concurrent programs, with a focus on the C11 memory model.

- The C11 model is highly complex. It has been formalized, but it was originally designed by the standards committee based on what seemed reasonable to implement at the time. It is natural to wonder whether it respects some basic intuitions: is it sound to replace a relaxed atomic (that is supposed to have the weakest guarantees) by a stronger one (monotonicity)? Is it sound to decompose a complex computation into several simpler ones with temporary variables? We answer these questions and others by the negative in Chapter 3, and propose modifications to the model that fix some of these warts.

- In Chapter 4, we study which traditional compiler optimisations designed in a sequential world remain correct in the C11 model. As expected, they remain correct on code without atomics, but must be very careful when modifying code containing atomics. We prove the correctness of criteria under which they remain sound.

- Armed with this theory of correct optimisations, we built a tool that uses random testing to find mistakes in the implementation of the C11 memory model in GCC. This tool is presented in Chapter 5.

- Another important question related to the C11 model is how usable it is in practice for writing complex lock-free algorithms. What patterns are the most frequently used? Can non-trivial code using atomic operations be proven correct? To answer these questions, we designed and implemented a dynamic scheduler for Kahn Process Networks in C11, starting from a naive sequentially consistent algorithm and progressively refining it to use more efficient atomic operations (Chapter 6).

- Finally, we looked at how compilers can optimize the fence instructions that they have to insert around atomic operations to prevent reorderings of instructions by the processor. We propose a novel algorithm for fence elimination based on Partial Redundancy Elimination (Chapter 7).

- Before all of that, we need to provide some background information. In particular, we will see formal models for x86, ARM, Power, and C11 (Chapter 2). This chapter includes some original work in Section 2.3.1, that shows how a compiler optimisation is unsound in the Power model.

**Collaborations** Much of the work presented in this thesis was done in collaboration with others and resulted in publications:

• The study and testing of the optimisations done by Clang and GCC around atomics was done with Pankaj Pawan and Francesco Zappa Nardelli. It was presented at PLDI 2013 [MPZN13] and is described in Section 4.1 and Chapter 5

- The formal study of optimisations in C11 and its variants was done with Viktor Vafeiadis, Thibaut Balabonski, Soham Chakraborty and Francesco Zappa Nardelli. It was presented at POPL 2015 [VBC+15] and is described in Chapter 3 and Section 4.2

- LibKPN (Chapter 6) was joint work with Nhat Minh Lê, Adrien Guatto and Albert Cohen. It has not yet been published.

- The fence elimination algorithm presented in Chapter 7 was designed during an internship at Google under the supervision of Jean-François Bastien and evaluated later with Francesco Zappa Nardelli. It will be presented at CC 2017 [MZN17].

## Chapter 2

## A primer on memory models

## 2.1 Examples of non-sequentially consistent behaviors

We already saw in the introduction the SB pattern (Figure 1.1), and how it can be caused by First-In First-Out (FIFO) store buffers in each core.

This is not the only processor optimisation that can be observed by multi-threaded programs. Consider for example the program in Figure 2.1, called *Message Passing* or MP in the literature:

Initially,

$$x = y = 0$$

$x := 1;$  if  $(y == 1)$

$y := 1;$  print  $x;$

Figure 2.1: Message Passing (MP) pattern

According to the SC model, this pattern should never print 0. And indeed it never does on x86, as the store buffers behave in a First-In First-Out (FIFO) way, so by the time the store of y is visible to the second thread, so is the store of x. But on ARM and Power, it will occasionally print 0. Several architectural reasons can explain this. For example, it could be that the store buffers are not FIFO, letting the store of y reach global memory before the store of x. Or this behaviour could be caused by speculation: the second core may guess that the branch will be taken, and execute the load of x in advance, possibly even before the load of y.

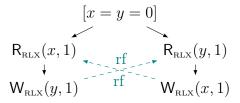

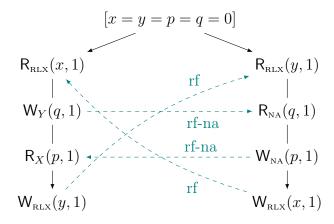

Another example is the *Load Buffering* (LB) pattern in Figure 2.2. Like the previous one, this program cannot print two ones in the SC model or on x86 processors, but it can on ARM and Power processors. This can be caused by the processors executing the

Figure 2.2: Load Buffering (LB) pattern

instructions out-of-order and deciding to execute the stores before the loads.

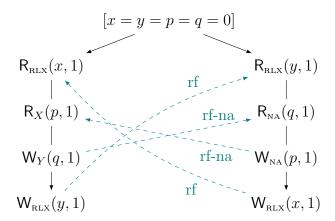

An even more surprising example is the *Independent Reads of Independent Writes* (IRIW) pattern in Figure 2.3.

Initially,

$$x = y = 0$$

$x := 1;$

$print x;$

$print y;$

$print x;$

$print x;$

$print x;$

$print x;$

Figure 2.3: Independent Reads of Independent Writes (IRIW) pattern

This is yet another case where x86 follows the SC model, but ARM and Power do not. More precisely, different cores can see the stores to x and y happening in different orders, resulting in both central threads printing 1 and then 0. This can happen if the L2 cache is shared between the threads 0 and 1, and is shared between the threads 2 and 3: the store of x will be visible first to the thread 1, and the store of y will be visible first to the thread 2.

Cache coherency is usually defined as all cores agreeing on the order in which all stores to each individual memory location reach the memory. While the behaviour shown above is quite unintuitive, it is not a violation of cache coherency: it is only the order of stores to different locations that is not well defined.

## 2.2 Hardware memory models

Given the wide range of surprising behaviours shown in Section 2.1 it is necessary for any programmer writing concurrent code in assembly to have a model of the observable effects of these processor optimisations. Processor vendors offer informal specifications in their programming manuals, but these are often ambiguous and sometimes outright incorrect. This led to a significant amount of research in formal memory models for hardware architectures.

#### 2.2.1 The x86 architecture

As we saw in Section 2.1, x86 differs from sequential consistency mostly by its behaviour in the SB pattern. It is possible to limit the behaviour in this pattern to those admissible under SC by inserting a special instruction called mfence between the stores and the loads. x86 also has a LOCK prefix that can be added to some instructions to make them atomic.

The x86 architecture is one of the first whose memory model was rigorously formalized and validated against the hardware. The resulting model is called x86-TSO and is described in [OSS09, SSO<sup>+</sup>10]. This model was formalized in two different ways, an operational and an axiomatic models. We describe both in more details below, as an example of each kind of model.

#### 2.2.1.1 The x86 operational model

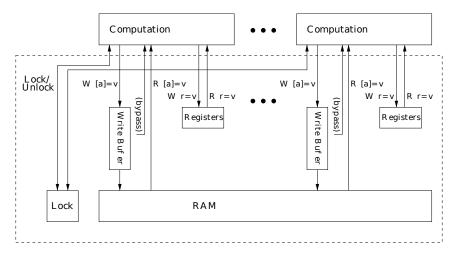

The first model is an *operational model* [BP09]: it is the description of an abstract machine that simulates an x86 processor and explicitly models the store buffers and a global lock.

Figure 2.4: Abstract machine for x86-TSO from [OSS09]

Such a model is convenient for building an intuition, and can easily show that a behaviour is possible. Unfortunately, showing a behaviour to be impossible can be difficult as all transitions must be explored.

In this view of x86-TSO, each processor proceeds mostly independently and completely sequentially, communicating with its store buffer, the global lock and the memory according to the following rules (see Figure 2.4):

- Whenever it executes a store, the store is sent to a local store buffer that acts as a First-In First-Out (FIFO) queue.

- Whenever it executes a load, it first checks if there is a store to the same address in the local store buffer. If there is, it returns the value of the latest such store. Otherwise it asks the global memory for the value of this memory location. In both cases, the load is only executed if the global lock is not taken by another processor.

- Whenever it executes an instruction with the LOCK prefix, it first flushes its local store buffer to memory, then takes the global lock, executes the instruction, flushes the buffer again, and release the lock afterwards. In x86, instructions with the LOCK prefix are executed atomically, and are used to implement primitives like fetch-and-add or compare-and-swap.

- Whenever it executes a mfence instruction, it flushes its local buffer.

- It can flush the latest store(s) from its buffer to the shared memory at any point where no other processor holds the global lock.

Consider again the SB example (Figure 1.1). Without fences, the following behaviour is permitted by the model:

- 1. The left thread sends the store to x to its store buffer.

- 2. It then executes the load of y. Since there is no store to y in its store buffer, it reads the initial value from global memory and prints 0.

- 3. The right thread sends the store to y to its store buffer.

4. The right thread executes the load of x. Since the store of x is only in the left thread's core's store buffer, it reads the initial value of x from global memory and prints 0.

With the mfence instruction added between every store and load, this execution would be impossible: the left thread would have to flush its store buffer to memory before executing the load. When the right thread later reads from memory, it would see the correct value and print 1.

However, note that in this model the only way to check that a behaviour can not happen (for example both thread printing 0) is to explore every transition of the system exhaustively.

#### 2.2.1.2 The x86 axiomatic model

The second model of x86-TSO is an *axiomatic model*: an execution is valid and can happen if there exists a set of relations between the memory accesses of the execution that verifies some set of axioms. The model is entirely defined by its relations and axioms.

Axiomatic models are usually less intuitive than operational ones, but easier to use for verification purposes [AKT13], as they simplify proofs that a behaviour is impossible.

Here is how the axiomatic formalisation of x86-TSO works in more detail. For each thread, the set of memory events (store, loads, locked operations) this thread can produce is generated, assuming completely arbitrary values returned for each read. The data of such a set and the program order relation (po) is called an event structure in [OSS09], but we will call it a *event set* here, as the term event structure has come to mean something else in more recent papers.

An event set is a valid execution if there exists an execution witness made of two relations reads-from (rf) and memory-order  $(mo)^1$  which respects the following axioms:

- 1. rf is a function from loads to store, and if w = rf(r), then w and r share the same value and memory location;

- mo is a partial order on memory events that is a total order on the stores to each memory location (but does not necessarily relate stores to different memory locations);

- 3. if  $w = \mathsf{rf}(r)$ , then there is no other write  $w_2$  to the same location with  $w <_{\mathsf{mo}} w_2$  and  $w_2 <_{\mathsf{mo}} r$  or  $w_2 <_{\mathsf{po}} r$ ;

- 4. program order is included in memory order for all of the following cases:

- the first event is a read,

- both events are writes,

- the first event is a write, the second is a read, and there is a mfence instruction in-between,

- one of the event comes from a locked instruction;

- 5. all memory events associated to a given locked instruction are adjacent in memory order.

<sup>&</sup>lt;sup>1</sup>The original model also includes an initial\_state function that we ignore for simplicity

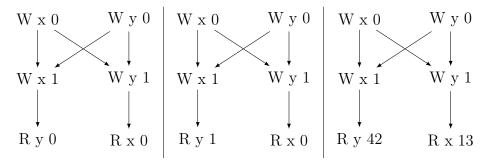

Consider again the SB example (Figure 1.1). It has a very large number of event sets, as we must generate one for every value that each load could read, for example those in Figure 2.5:

Figure 2.5: Three examples (out of many) of event sets of SB. Note the arbitrary values returned by reads.

For each of these we can try building mo and rf. In particular, to check that SB can print two 0, we must build these two relations for the corresponding event set. We clearly can, as shown in Figure 2.6 where all the axioms are respected.

Figure 2.6: building mo and rf for the anomalous SB result

This might not look like an improvement over the operational model. But it becomes useful when we try to show that some behaviour *cannot* happen. For instance, we can now easily show that SB cannot print two 0 with a mfence between the store and the load in each thread. By the axiom 4, the events in each thread are necessarily ordered by mo. And they are mo-after the initial stores. We assume the existence of the initial stores that are po-before all other events to avoid having to special-case them. By the Axiom 1, each read must be related by rf to the initial stores. But that is in contradiction with Axiom 3: we have successfully proven that adding a mfence between the stores and the loads prevent this program from printing two 0.

A complete description of the models can be found in the aforementioned papers.

#### 2.2.2 The Power and ARM architectures

A memory model is said to be stronger than another one if it allows less behaviours. SC is clearly the strongest of all the memory models we saw. As we saw earlier with the MP, LB and IRIW examples, both Power and ARM have significantly weaker memory models than x86.

These models are highly subtle and poorly documented, which led to a list of progressively more complete and readable formalisations in the literature [AFI<sup>+</sup>09, AMSS10, SSA<sup>+</sup>11, SMO<sup>+</sup>12, MMS<sup>+</sup>12, AMT14]. We will only present in detail the formalization in [AMT14], which we rely upon in Chapter 7. This model <sup>2</sup> is axiomatic, and we call it the "Herding Cats" model after the title of the paper.

This formalisation is actually a framework with several parameters that can be instantiated to give a model for Power, ARM, x86 or even SC.

In this framework the semantics of a program is defined in three steps, as in the x86 axiomatic model.

First the program is mapped to a set of memory events (e.g. atomic read or writes of shared memory locations) and several relations among these events. The intuition is that these events capture all possible memory accesses performed by the various threads running in an arbitrary concurrent context. The additional relations capture how several "syntactic" aspects of the source program lift to, and relate, events. These include the program order relation (po), that lifts the program order to the events, and the addr, data, and ctrl relations, that lift address, data and control dependencies between instructions to events. This corresponds to the event sets in the model of Section 2.2.1.2

Second, candidate executions are built out of the events by imposing restrictions on which values read events can return, each execution capturing a particular data-flow of the program. The restriction are expressed via two relations, called reads-from (rf) and coherence-order (co). The former associates each read even to the write event it observes. The second imposes a per-location total order on memory writes, capturing the base property ensured by cache coherence. These are subject to two well-formedness conditions:

- rf is a function from loads to store, and if w = rf(r), then w and r share the same value and memory location;

- co is a partial order on memory events that is a total order on the stores to each memory location (but does not necessarily relate stores to different memory locations).

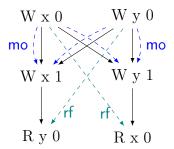

Several auxiliary relation are computed out of rf and co. The most important is the relation from-read (fr), defined as  $rf^{-1}$ ; co, that relates a read to any store that is co-after the one it reads from. An example of that can be seen in Figure 2.7: because the load of x reads from the first store, it is related by fr to every later store to x.

We also compute the projections of rf, fr and co to the events internal to a thread (the related events belong to the same thread, suffix i) or external (the related events belong to different threads, suffix e) to a thread; these are denoted rfi, rfe, fri fre and coe. The construction of these relations corresponds to the construction of rf and mo in the model of Section 2.2.1.2, with co corresponding to mo.

Third, a constraint specification decides if a candidate executions are valid or not. HerdingCats is a framework that can be instantiated to different architectures. For this it is parametric in two relations happens-before (hb), defining the relative ordering of

$<sup>^2{\</sup>rm This}$  model does not cover mixed-size accesses, nor special instructions like load-linked/store-conditional

Figure 2.7: co, rf, and fr

the events., and *propagation order* (prop), capturing the relative ordering of memory writes to different locations that somehow synchronise. We detail the instantiation of the framework to x86, Power, and ARM below. The framework then imposes only four axioms on candidate executions to determine their validity. These axioms play the same role as the axioms of the model of Section 2.2.1.2

The first axiom, **SC PER LOCATION**, captures cache coherence: for every memory location considered in isolation, the model behaves as if it was sequentially consistent. In formal terms:

$$acyclic(poloc \cup com)$$

where poloc is the program order restricted per location, and com (communication order) is the union of the coherency order co, the reads-from relation rf, and the from-reads relation fr.

The second axiom, **NO THIN AIR**, prevents the so-called *out-of-thin-air reads*, where the read of a value is justified by a store that is itself justified by the original read. Such causality loops are not observable on any modern hardware. In Section 3.1.2 we will see how troublesome a model without that rule is. In formal terms, the rule forbids cycles in *happens-before* (hb), which is the first parameter of the model:

The third axiom, **OBSERVATION**, mostly enforces that loads cannot read from stores that have been overwritten in-between. In particular, it is what makes the MP(Figure 2.1) pattern work in x86, and with the right fences in ARM and Power too.

In this rule fre is the restriction of fr to an inter-thread relation, hb\* is the transitive and reflexive closure of hb, and prop is the second parameter of the model. The stated justification in the paper for prop is to relate stores to different memory locations that are synchronised somehow, and thus represent *cumulativity*. In the words of the paper, "a fence has a cumulative effect when it ensures a propagation order not only between writes on the fencing thread (i.e. the thread executing the fence), but also between certain writes coming from threads other than the fencing thread." [AMT14, p. 18].

The fourth axiom, **PROPAGATION**, enforces the compatibility of the coherence order with this **prop** relation:

In fact, prop is not entirely limited to stores on Power (see below), and has a term that can relate loads. It is this term in combination with the propagation axiom that bans the IRIW pattern (Figure 2.3) when the loads are separated by heavyweight fences.

#### 2.2.2.1 Instantiations of the framework

The model presented above is completely generic over **hb** and **prop**. We will now show what definition to give to these two relations to make the model describe different architectures.

Instantiation for SC Getting back sequential consistency in this framework is easy: just define  $hb = po \cup rfe$  and  $prop = po \cup rf$  (where rfe is the restriction of rf to an inter-thread relation). Then the first three axioms are implied by the fourth one which is equivalent to  $acyclic(po \cup com)$ , which is a well-known characterisation of SC [Lam79].

Instantiation for x86 Similarily, x86-TSO can be recovered by defining  $hb = po \WR \cup mfence \cup rfe$  and  $prop = hb \cup fr$ , with mfence being the restriction of po to pairs of accesses with a mfence instruction in between, and  $po \WR$  the program order relation from which every pair from a write to a read has been removed. In this instantiation, the axioms NO THIN AIR and OBSERVATION are implied by PROPAGATION.

**Instantiation for Power** The Power memory model is significantly more complex. Here are the definitions of hb and prop:

```

(Iwsync \setminus WR) \cup hwsync

fences

rfe?; fences; hb*

propbase

prop

(propbase \cap WW) \cup (com^*; propbase^*; hwsync; hb^*)

def

dp

addr ∪ data

rdw

poloc \cap (fre; rfe)

detour

poloc \cap (coe; rfe)

dp \cup rdw \cup rfi

ii_0

ci_0

(\mathsf{ctrl} + \mathsf{cfence}) \cup \mathsf{detour}

ic_0

def

dp \cup poloc \cup ctrl \cup (addr; po)

cc_0

\stackrel{\mathsf{def}}{=} \ ii_0 \cup ci \cup (ic; ci) \cup (ii; ii)

ii

\stackrel{\mathsf{def}}{=} \ ci_0 \cup (ci; ii) \cup (cc; ci)

ci

\stackrel{\mathsf{def}}{=} ic_0 \cup ii \cup cc \cup (ic; cc) \cup (ii; ic)

ic

\stackrel{\mathsf{def}}{=} \ cc_0 \cup ci \cup (ci; ic) \cup (cc; cc)

cc

\stackrel{\mathsf{def}}{=} \ (ii \cap \mathsf{RR}) \cup (ic \cap \mathsf{RW})

ppo

hb

ppo \cup fences \cup rfe

```

In these, lwsync and hwsync are restrictions of po to pairs of accesses with respectively a lwsync or hwsync (two kinds of fence instruction that exist on Power, respectively lightweight and heavyweight synchronisation) in between. ctrl, addr and data are respectively control, address and data dependencies. Finally, ctrl + cfence refers to control dependencies which have been reinforced by an isync fence.

The relations ii, ic, ci cc are defined as the least fixed point of the equations above. The intuition behind these is that i stands for "initiation" of an access, while c stands for "commit" of an access; which is similar to older models for Power [MMS<sup>+</sup>12].

**Instantiation for the ARM architecture** The instantiation of HerdingCats for ARM follows the IBM Power one, with three differences:

- the relation hwsync is replaced by the relation dmb ish, that is the restriction of po to pairs of accesses with respectively a dmb ish synchronising barrier in between; similarly the relation cfence is replaced by the relation isb, that is the restriction of po to pairs of accesses with respectively a isb instruction in between;

- the relation lwsync is removed;

- the relation  $cc_0$  is redefined as  $dp \cup ctrl \cup (addr; po)$ , losing the poloc term (the reason for this is detailed at length in [AMT14]).

#### 2.2.3 Other architectures

Several other architectures have complex and documented memory models: Alpha [alp98], Itanium [ita02], Sparc [WG03]. Because these architectures are not as popular as x86 and ARM, we do not consider them in the rest of this thesis. We also do not treat GPUs, whose memory model has only started to be studied over the past few years.

I would like to mention one point about Alpha however: it is an example of how weak a hardware memory model can be. In particular it is the only architecture that does not respect address dependency by default between reads: the pseudo-code (using the C notation for pointers) in Figure 2.8 can print 0:

Figure 2.8: Example of an address dependency

It is as if the load of \*y was reordered before the load of y. This could be caused by using independent caches for different cache lines, and in particular for y and x.

## 2.3 Language memory models

As we saw in Chapter 1, languages must also have a memory model that describes both how the optimisations done by the compiler can change the semantics of concurrent programs and what fences it introduces to restrict the underlying processor from doing the same.

```

Initially, x = y = z = 0

r0 = z;

print r0; // 42

z := 42;

z := 13;

sync;

x := 42;

z := r1;

sync;

y := 1;

```

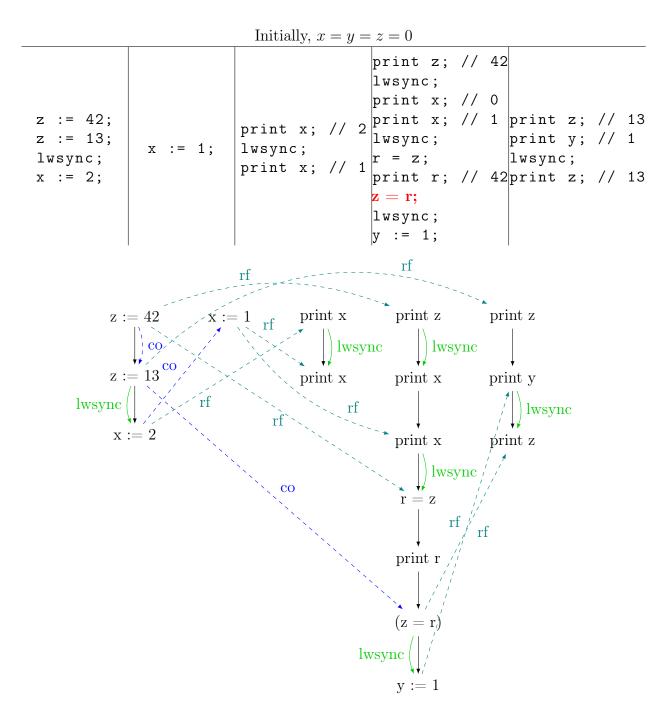

Figure 2.9: WaR elimination in the Power model: counterexample with a dependency

#### 2.3.1 Compiler optimisations in the Power model?

Since hardware memory models are reasonably well understood, it is tempting to lift one of them to the language level. We want a weak one, to allow many compiler optimisations. Since Power has one of the weakest hardware models that has been extensively studied, it is the obvious pick.

In this section we show why it is not a good option: some common compiler optimizations are unsound in the Power memory model<sup>3</sup>.

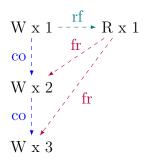

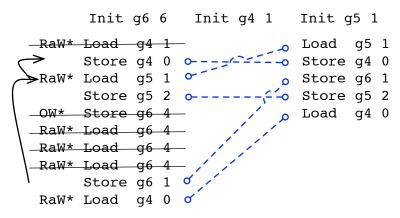

In particular, one of the optimizations we study in Chapter 4 is called *Write-after-Read* elimination (WaR) in the literature, and consists in eliminating a store to memory when the value stored has just been read.

Figure 2.9 provides a counterexample to the claim that WaR elimination is sound in the Power model: it is impossible to have all the print instructions give the expected result before the highlighted store (in bold and red) is removed and it becomes possible afterwards. Compilers could try to remove this store because it is only executed when the value to be stored is equal to the value that was just read, so it seems unable to modify the state of memory. The synchronisation on x makes the stores to z to happen before the highlighted store. That store, in turn, happens before the load of z in the last thread. As a result, this load can not see the store of 13, as it is overwritten by the highlighted store with the value 42. If that store is removed, the printing of 13 suddenly becomes possible.

It might seem that this example relies on the dependency between the load and the store, and that we could find some local criterion under which WaR elimination is valid on Power, such as an absence of dependency between the load and the store.

Figure 2.10 proves that there is no local condition sufficient to make WaR elimination sound: even when the store to be eliminated is adjacent to the load that justifies it, it is still unsound to remove it. Like in the previous example, the print operations can only give the results in the comments if the highlighted access is removed, so removing it is unsound. This counterexample was carefully checked both by hand and by an unreleased software tool by Luc Maranget. Here is some intuition for how it works. The synchronisation on  $\mathbf{y}$  between the last two threads ensures that the to-be-eliminated access is visible to the last load of  $\mathbf{z}$  in the last thread. The complex synchronisation on  $\mathbf{x}$  in the first 4 threads ensures that this second store of 42 in  $\mathbf{z}$  is after the store of 13 in the coherency order.

<sup>&</sup>lt;sup>3</sup>This section presents original work, by opposition to the rest of this chapter that only provides background.

Figure 2.10: WaR elimination in the Power model: counterexample in the most general case

We use this complex pattern instead of a simpler message-passing pattern to allow the last load of 42 in the second to last thread.

#### 2.3.2 Data-Race Freedom (DRF)

A fairly simple and popular language-level memory model is Data-Race Freedom (DRF) [AH90].

A data-race is described as two memory events, one of which at least is a write, accessing the same memory location concurrently. DRF states that every program that is free from data-races on all of its executions (and in particular any program that protects all of its concurrently accessed locations by locks) behaves as it would in the SC model. Any data-race is undefined behaviour, and any program that can exhibit one has no defined semantics.

This model is attractive for three reasons:

- it is rather easy to explain to programmers;

- common compiler optimisations remain correct on any piece of code without locks [Sev11, Sev08];

- fence instructions, that limit the optimisations performed by the processor, only have to be introduced inside the lock and unlock methods.

However, the fact that this model gives no defined semantics to racy code is a major weakness. It makes it unsuitable for use by both Java and C/C++, although for different reasons.

It is unsuitable to Java, because racy code can break safety invariants (since by definition it can do absolutely anything). This is unacceptable for Java, as no valid Java code should be able to forge a pointer to the internals of the JVM. As a result, the Java community had to develop a much more complex memory model [MPA05]. This model evolved over the years as some flaws were discovered (see for example [SA08]). As we are focused on the C11 model in the rest of this thesis, we won't describe it here.

C and C++ cannot use DRF either, because of the second weakness: it is impossible to write low-level racy code in the DRF model, as all concurrent accesses must be protected by some synchronisation. To solve this problem, C and C++ use a variant of DRF, where some accesses can be annotated by the programmer to allow races involving them. Such *atomic accesses* have a behaviour that is complex and dependent on the annotation provided by the programmer. We will now explain this model in more details.

## 2.3.3 The C11/C++11 model

The C11/C++11 memory model was first presented in the C++11 standard [Bec11]. It offers four kind of operations:

- stores;

- loads;

- read-modify-write (RMW) operations like compare-and-swap (CAS) or fetch-and-add;

• fences.

Each store and load is either not annotated and called not-atomic (NA), or annotated with one of the following *memory orders* (also called memory attributes):

- Sequentially consistent (SC): all such accesses are fully ordered. If all concurrent accesses in a program have this attribute, then the program follows the SC model;

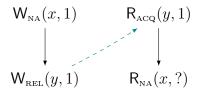

- Release (REL, for writes) and Acquire (ACQ, for reads) enforce the SC behavior specifically in the MP pattern. Anything that happens before a release store is visible to anything that happens after an acquire load that reads from that store. For example, in the following figure, the non-atomic load must read the value 1:

- Consume (CONSUME, for reads only) is a weaker form of acquire: it only prevents the MP pattern anomaly if the second read has an address dependency on the first one. It was introduced to the standard to avoid a fence in that specific case on ARM and Power;

- Relaxed (RLX) accesses offer extremely few guarantees, mostly just cache coherency. They are intended not to require hardware fences on any common architecture, and only weakly restrict compiler optimisations.

Similarly, RMW operations can be SC, REL, ACQ, CONSUME, RLX, or Release-Acquire (REL-ACQ) which combine the properties of REL and ACQ.

Fences can also have one of several memory orders:

- REL fences make subsequent relaxed stores behave more like release stores (we will soon see a more rigorous description, this is only the intuition behind them);

- ACQ fences make previous relaxed loads behave more like acquire loads;

- REL-ACQ fences naturally behave like both release and acquire fences;

- SC fences additionally prevent the anomalous behavior of the SB pattern.

We will now give the details of the formalisation of C11, that was first given in [BOS<sup>+</sup>11] and was further extended in [BMO<sup>+</sup>12].

Like the other axiomatic models we have seen, it is organised in three steps. First it builds sets of events (called opsems below), then it considers possible relations between those events (these set of relations are called witnesses below), and finally it filters all these candidate executions by some axioms.

**Opsemsets** To abstract from the syntax complexity of the C language, we identify a source program with a set of descriptions of what *actions* it can perform when executed in an arbitrary context.

More precisely, in a source program each thread consists of a sequence of *instructions*. We assume that, for each thread, a thread-local semantics associates to each *instruction instance* zero, one, or more shared memory accesses, which we call *actions*. The actions we consider, ranged over by *act*, are of the form:

$$\begin{split} \Phi &::= \mathsf{skip} \mid \mathsf{W}_{(\mathsf{SC}|\mathsf{REL}|\mathsf{RLX}|\mathsf{NA})}(\ell,v) \mid \mathsf{R}_{(\mathsf{SC}|\mathsf{ACQ}|\mathsf{RLX}|\mathsf{NA}|\mathsf{CONSUME})}(\ell,v) \\ & \mid \mathsf{C}_{(\mathsf{SC}|\mathsf{REL-ACQ}|\mathsf{ACQ}|\mathsf{REL}|\mathsf{RLX})}(\ell,v,v') \mid \mathsf{F}_{(\mathsf{ACQ}|\mathsf{REL}|\mathsf{REL-ACQ}|\mathsf{SC})} \mid \mathsf{A}(\ell) \\ & act ::= tid : \Phi \end{split}$$

where  $\ell$  ranges over memory locations, v over values and  $tid \in \{1..n\}$  over thread identifiers. We consider atomic and non-atomic loads from (denoted R) and stores to (W) memory, fences (F), read-modify-writes (C), and allocations (A) of memory locations. To simplify the statement of some theorems, we also include a no-op ( $\mathsf{skip}$ ) action. Each action specifies its thread identifier tid, the location  $\ell$  it affects, the value read or written v (when applicable), and the memory-order (written as a subscript, when applicable).

We assume a labelling function, lab, that associates action identifiers (ranged over by  $a, b, r, w, \ldots$ ) to actions. In the drawings we usually omit thread and action identifiers.

We introduce some terminology regarding actions. A read action is a load or a read-modify-write (RMW); a write is a store or a RMW; a memory access is a load, store or RMW. Where applicable, we write  $\mathsf{mode}(a)$  for the memory order of an action,  $\mathsf{tid}(a)$  for its thread identifier, and  $\mathsf{loc}(a)$  for the location accessed. We say an action is non-atomic if and only if its memory-order is NA, and SC-atomic if and only if it is SC. An acquire action has memory-order ACQ or stronger, while a release has REL or stronger. The is stronger relation, written  $\square$ :  $\mathcal{P}(MO \times MO)$ , is defined to be the least reflexive and transitive relation containing SC  $\square$  REL-ACQ  $\square$  REL  $\square$  RLX, and REL-ACQ  $\square$  ACQ  $\square$  CONSUME  $\square$  RLX.

The thread local semantics captures control flow dependencies via the sequenced-before (sb) relation, which relates action identifiers of the same thread that follow one another in control flow. We have sb(a,b) if a and b belong to the same thread and a precedes b in the thread's control flow. Even among actions of the same thread, the sequenced-before relation is not necessarily total because the order of evaluation of the arguments of functions, or of the operands of most operators, is underspecified in C and C++.

The thread local semantics also captures thread creation via the *additional-synchronised-with* (asw) relation, that orders all the action identifiers of a thread after the corresponding thread fork (which can be represented by a skip action).

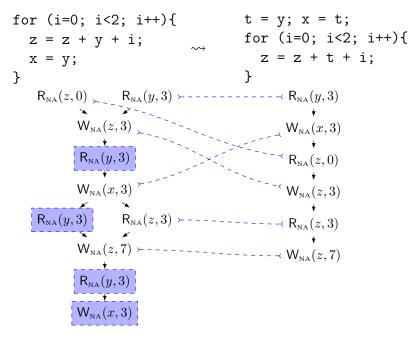

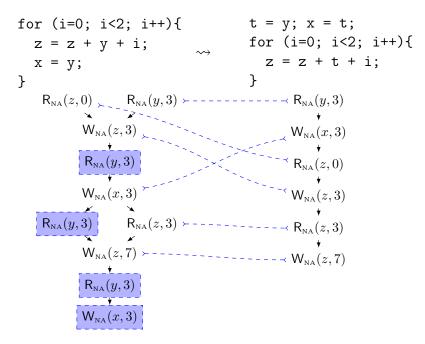

Summarising, the thread local semantics gives each program execution a triple O = (lab, sb, asw), called an *opsem*. As an example, Figure 2.11 depicts one opsem for the program on the left and one for the program on the right. Both opsems correspond to the executions obtained from an initial state where y holds 3, and the environment does not perform any write to the shared variables (each read returns the last value written).

The set of all the opsems of a program is an *opsemset*, denoted by S. We require opsemsets to be *receptive*: S is receptive if, for every opsem O, for every read action r in the opsem O, for all values v' there is an opsem O' in S which only differs from O because the read r returns v' rather than v, and for the actions that occur after r in  $sb \cup asw$ . Intuitively an opsemset is receptive if it defines a behaviour for each possible value returned by each read.

Figure 2.11: Example of the effect of a code transformation (Loop Invariant Code Motion) on an opsem (in which initially y = 3 and z = 0)

We additionally require opsemsets to be prefix-closed, assuming that a program can halt at any time. Formally, we say that an opsem O' is a prefix of an opsem O if there is an injection of the actions of O' into the actions of O that behaves as the identity on actions, preserves sb and asw, and, for each action  $x \in O'$ , whenever  $x \in O$  and  $(sb \cup asw)(y, x)$ , it holds that  $y \in O'$ .

Opsems and opsemsets are subject to several other well-formedness conditions, e.g. atomic accesses must access only atomic locations, which we omit here and can be found in [BOS<sup>+</sup>11].

Candidate executions The mapping of programs to opsemsets only takes into account the structure of each thread's statements, not the semantics of memory operations. In particular, the values of reads are chosen arbitrarily, without regard for writes that have taken place.

The C11 memory model then filters inconsistent opsems by constructing additional relations and checking the resulting candidate executions against the axioms of the model. We present here a subset of the model, without CONSUME for simplicity. We will see in Section 3.0.1 that consume is effectively unusable with its current definition. For the subset of C11 we consider, a witness W for an opsem O contains the following additional relations:

- The reads-from map (rf) maps every read action r to the write action w that wrote the value read by r.

- The modification-order (mo) relates writes to the same location; for every location, it is a total order among the writes to that location.

- The sequential-consistency order (sc) is a total order over all SC-atomic actions. (The standard calls this relation S.)

From these relations, C11 defines a number of derived relations, the most important of which are: the *synchronizes-with* relation and the *happens-before* order.

```

\operatorname{isread}_{\ell,v}(a) \stackrel{\mathsf{def}}{=} \exists X, v'. \ lab(a) \in \{\mathsf{R}_X(\ell,v), \mathsf{C}_X(\ell,v,v')\}

\operatorname{isread}_{\ell}(a) \stackrel{\mathsf{def}}{=} \exists v. \operatorname{isread}_{\ell,v}(a)

\operatorname{isread}(a) \stackrel{\mathsf{def}}{=} \exists \ell. \operatorname{isread}_{\ell}(a)

\mathsf{iswrite}_{\ell,v}(a) \stackrel{\mathsf{def}}{=}

\exists X, v'. \ lab(a) \in \{ \mathsf{W}_X(\ell, v), \mathsf{C}_X(\ell, v', v) \}

\mathsf{iswrite}_\ell(a) \stackrel{\mathsf{def}}{=}

\exists v. \text{ iswrite}_{\ell,v}(a)

\mathsf{iswrite}(a) \stackrel{\mathsf{def}}{=}

\exists \ell. \text{ iswrite}_{\ell}(a)

isfence(a) \stackrel{\mathsf{def}}{=}

lab(a) \in \{\mathsf{F}_{\scriptscriptstyle{\mathrm{ACQ}}}, \mathsf{F}_{\scriptscriptstyle{\mathrm{REL}}}, \mathsf{F}_{\scriptscriptstyle{\mathrm{REL-ACQ}}}, \mathsf{F}_{\scriptscriptstyle{\mathrm{SC}}}\}

\mathsf{isaccess}(a) \stackrel{\mathsf{def}}{=}

isread(a) \lor iswrite(a)

\mathsf{isNA}(a) \stackrel{\mathsf{def}}{=}

\mathsf{mode}(a) = \mathsf{NA}

sameThread(a, b) \stackrel{def}{=}

\mathsf{tid}(a) = \mathsf{tid}(b)

\mathsf{isrmw}(a) \stackrel{\mathsf{def}}{=}

isread(a) \land iswrite(a)

isSC(a) \stackrel{\mathsf{def}}{=}

\mathsf{mode}(a) = \mathsf{SC}

rsElem(a, b) \stackrel{def}{=}

sameThread(a, b) \lor isrmw(b)

\mathsf{isAcq}(a) \stackrel{\mathsf{def}}{=}

\mathsf{mode}(a) \sqsupset \mathsf{ACQ}

isRel(a) \stackrel{\text{def}}{=}

\mathsf{mode}(a) \sqsupset \mathsf{REL}

rseq(a, b) \stackrel{def}{=}

a = b \vee \mathsf{rsElem}(a, b) \wedge mo(a, b) \wedge (\forall c. \ mo(a, c) \wedge mo(c, b) \Rightarrow \mathsf{rsElem}(a, c))

\mathsf{sw}(a,b) \stackrel{\mathsf{def}}{=} \ \exists c,d. \ \neg \mathsf{sameThread}(a,b) \land \mathsf{isRel}(a) \land \mathsf{isAcq}(b) \land \mathsf{rseq}(c,\mathit{rf}(d)) \\ \land (a=c \lor \mathsf{isfence}(a) \land \mathit{sb}^+(a,c)) \land (d=b \lor \mathsf{isfence}(d) \land \mathit{sb}^+(d,b))

\mathsf{hb} \stackrel{\mathsf{def}}{=} (sb \cup \mathsf{sw} \cup asw)^+

\mathsf{Racy} \stackrel{\mathsf{def}}{=} \ \exists a,b. \stackrel{\mathsf{isaccess}(a)}{\wedge} \land \mathsf{isaccess}(b) \land \mathsf{loc}(a) = \mathsf{loc}(b) \land a \neq b \\ \land (\mathsf{iswrite}(a) \lor \mathsf{iswrite}(b)) \land (\mathsf{isNA}(a) \lor \mathsf{isNA}(b)) \land \neg (\mathsf{hb}(a,b) \lor \mathsf{hb}(b,a))

Observation <sup>def</sup>

\{(a,b) \mid mo(a,b) \land loc(a) = loc(b) = world\}

```

Figure 2.12: Auxiliary definitions for a C11 execution (lab, sb, asw, rf, mo, sc).

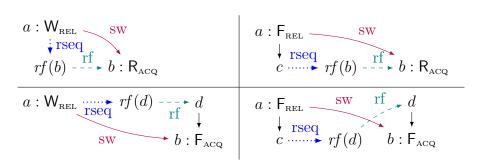

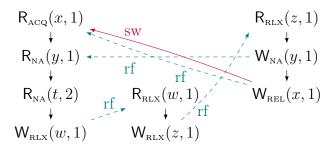

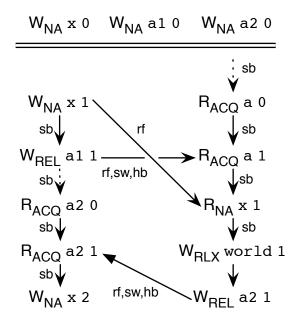

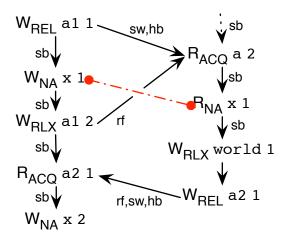

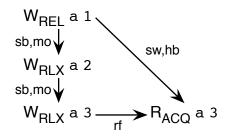

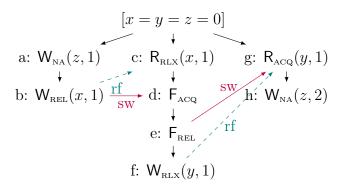

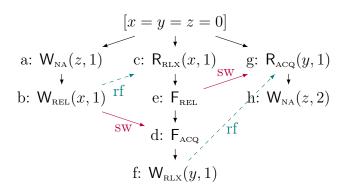

Figure 2.13: Illustration of the "synchronizes-with" definition: the four cases inducing an sw edge.

- Synchronizes-with (sw) relates each release write with the acquire reads that read from some write in its release sequence (rseq). This sequence includes the release write and certain subsequent writes in modification order that belong to the same thread or are RMW operations. The sw relation also relates fences under similar conditions. Roughly speaking, a release fence turns succeeding writes in sb into releases and an acquire fence turns preceding reads into acquires. (For details, see the definition in Figure 2.12 and the illustration in Figure 2.13.)

- Happens-before (hb) is a partial order on actions formalising the intuition that one action was completed before the other. In the C11 subset we consider,  $hb = (sb \cup sw \cup asw)^+$ .

We refer to a pair of an opsem and a witness (O, W) as a candidate execution. A candidate execution is said to be consistent if it satisfies the axioms of the memory model, which will be presented shortly. The model finally checks if none of the consistent executions contains an undefined behaviour, arising from a race (two conflicting accesses not related by  $hb)^4$  or a memory error (accessing an unallocated location), where two accesses are conflicting if they are to the same address, at least one is a write, and at least one is non-atomic. Programs that exhibit an undefined behaviour in one of their consistent executions are undefined; programs that do not exhibit any undefined behaviour are called well defined, and their semantics is given by the set of their consistent executions.

Consistent Executions. According to the C11 model, a candidate execution (lab, sb, asw, rf, mo, sc) is consistent if all of the properties shown in Figure 2.14 hold.

(ConsSB) Sequenced-before relates only same-thread actions.

(ConsMO) Writes on the same location are totally ordered by mo.

- (ConsSC) The sc relation must be a total order over SC actions and include both hb and mo restricted to SC actions. This in effect means that SC actions are globally synchronised.

- (ConsRFdom) The reads-from map, rf, is defined for exactly those read actions for which the execution contains an earlier write to the same location.

- (ConsRF) Each entry in the reads-from map, rf, should map a read to a write to the same location and with the same value.

- (ConsRFna) If a read reads from a write and either the read or the write are non-atomic, then the write must have happened before the read. Batty et al. [BOS+11] additionally require the write to be *visible*: i.e. not to have been overwritten by another write that happened before the read. This extra condition is unnecessary, as it follows from (CohWR).

- (SCReads) SC reads are restricted to read only from the immediately preceding SC write to the same location in sc order or from a non-SC write that has not happened before that immediately preceding SC write.

- (IrrHB) The happens-before order, hb, must be irreflexive: an action cannot happen before itself.

<sup>&</sup>lt;sup>4</sup> The standard distinguishes between races arising from accesses of different threads, which it calls *data races*, and from those of the same thread, which it calls *unsequenced races*. The standard says unsequenced races can occur even between atomic accesses.

```

\forall a, b. \ sb(a, b) \implies \mathsf{tid}(a) = \mathsf{tid}(b)

(ConsSB)

order(iswrite, mo) \land \forall \ell. total(iswrite_{\ell}, mo)

(ConsMO)

\operatorname{order}(\operatorname{isSC}, sc) \wedge \operatorname{total}(\operatorname{isSC}, sc) \wedge (\operatorname{hb} \cup mo) \cap (\operatorname{isSC} \times \operatorname{isSC}) \subseteq sc

(ConsSC)

\forall b. \ (\exists c. \ rf(b) = c) \iff \exists \ell, a. \ \mathsf{iswrite}_{\ell}(a) \land \mathsf{isread}_{\ell}(b) \land \mathsf{hb}(a,b)

(ConsRFdom)

\forall a, b. \ rf(b) = a \implies \exists \ell, v. \ \mathsf{iswrite}_{\ell,v}(a) \land \mathsf{isread}_{\ell,v}(b)

(ConsRF)

\forall a, b. \ rf(b) = a \land (\mathsf{isNA}(a) \lor \mathsf{isNA}(b)) \implies \mathsf{hb}(a, b)

(ConsRFna)

\forall a, b. \ rf(b) = a \land \mathsf{isSC}(b) \implies

(SCReads)

\mathsf{imm}(\mathsf{scr}, a, b) \vee (\neg \mathsf{isSC}(a) \wedge \nexists x. \, \mathsf{hb}(a, x) \wedge \mathsf{imm}(\mathsf{scr}, x, b))

\nexists a. \mathsf{hb}(a,a)

(IrrHB)

\nexists a, b. \quad rf(b) = a \wedge \mathsf{hb}(b, a)

(ConsRFhb)

\nexists a, b. \mathsf{hb}(a, b) \land mo(b, a)

(CohWW)

\not\exists a, b. \ \mathsf{hb}(a, b) \land mo(rf(b), rf(a))

(CohRR)

\nexists a, b. \ \mathsf{hb}(a, b) \land mo(rf(b), a)

(CohWR)

\nexists a, b. \mathsf{hb}(a, b) \land mo(b, rf(a))

(CohRW)

\forall a, b. \ \mathsf{isrmw}(a) \land rf(a) = b \implies \mathsf{imm}(mo, b, a)

(AtRMW)

\forall a, b, \ell. \ lab(a) = lab(b) = A(\ell) \implies a = b

(ConsAlloc)

\forall a, b, x. \ (\mathsf{isfence}(x) \land \mathsf{isread}(b) \land \mathsf{iswrite}_{\mathsf{loc}(b)}(a) \land

(SCFences1)

\mathsf{imm}(sc, a, x) \wedge sb^+(x, b) \implies (a = rf(b) \vee mo(a, rf(b)))

\forall a, b, x. \ (\mathsf{isfence}(x) \land \mathsf{isread}(b) \land \mathsf{iswrite}_{\mathsf{loc}(b)}(a) \land

(SCFences2)

sb^+(a,x) \wedge sc(x,b) \implies (a = rf(b) \vee mo(a,rf(b)))

\forall a, b, x, y. \ (\mathsf{isfence}(x) \land \mathsf{isfence}(y) \land \mathsf{isread}(b) \land \mathsf{iswrite}_{\mathsf{loc}(b)}(a) \land

(SCFences3)

sc(x,y) \wedge sb^{+}(a,x) \wedge sb^{+}(y,b) \implies (a = rf(b) \vee mo(a,rf(b)))

\forall a, b, x, y. \ (\mathsf{isfence}(x) \land \mathsf{isfence}(y) \land \mathsf{iswrite}(b) \land \mathsf{iswrite}_{\mathsf{loc}(b)}(a) \land

(SCFences4)

sc(x,y) \wedge sb^{+}(a,x) \wedge sb^{+}(y,b) \implies mo(a,b)

\forall a, b, y. \ (\mathsf{isfence}(y) \land \mathsf{iswrite}(b) \land \mathsf{iswrite}_{\mathsf{loc}(b)}(a) \land

(SCFences5)

sc(a,y) \wedge \wedge sb^+(y,b)) \implies mo(a,b)

\forall a, b, x. \ (\mathsf{isfence}(x) \land \mathsf{iswrite}(b) \land \mathsf{iswrite}_{\mathsf{loc}(b)}(a) \land

(SCFences6)

sc(x,b) \wedge sb^{+}(a,x) \wedge \implies mo(a,b)

where \operatorname{order}(P,R)\stackrel{\mathsf{def}}{=} (\nexists a.\ R(a,a))\ \wedge\ (R^+\subseteq R)\ \wedge\ (R\subseteq P\times P)

\operatorname{imm}(R, a, b) \stackrel{\mathsf{def}}{=} R(a, b) \wedge \nexists c. \ R(a, c) \wedge R(c, b)

\mathsf{total}(P,R) \stackrel{\mathsf{def}}{=} (\forall a,b.\ P(a) \land P(b) \implies a = b \lor R(a,b) \lor R(b,a))

\mathsf{scr}(a,b) \stackrel{\mathsf{def}}{=} sc(a,b) \wedge \mathsf{iswrite}_{\mathsf{loc}(b)}(a)

```

Figure 2.14: Axioms satisfied by consistent C11 executions, Consistent (lab, sb, asw, rf, mo, sc).

Figure 2.15: Patterns forbidden by the SCFences axioms.

(ConsRFhb) A read cannot read from a future write.

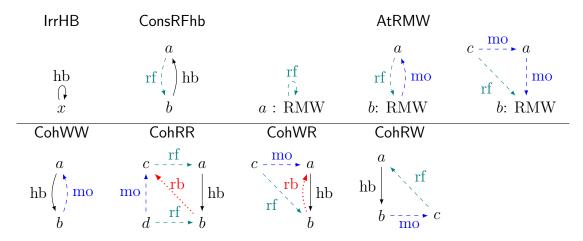

(CohWW, CohRR, CohWR, CohRW) Next, we have four coherence properties relating mo, hb, and rf on accesses to the same location. These properties require that mo never contradicts hb or the observed read order, and that rf never reads values that have been overwritten by more recent actions that happened before the read.

(AtRMW) Read-modify-write accesses execute atomically: they read from the immediately preceding write in mo.

(ConsAlloc) The same location cannot be allocated twice by different allocation actions. (This axiom is sound because for simplicity we do not model deallocation. The C11 model by Batty et al. [BOS+11] does not even model allocation.)

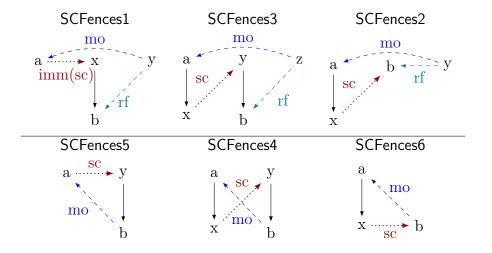

(SCFences1, SCFences2, SCFences3, SCFences4, SCFences5, SCFences6) These six properties explain in detail how SC fences restrict *mo* for writes nearby. More precisely they forbid the patterns shown in Figure 2.15.

## Chapter 3

# Issues with the C11 model and possible improvements

In this chapter we will list unintuitive consequences of the axioms of the C11 model, and propose improvements to the model where possible.

We will first explain some known difficulties related to consume accesses and SC fences. They led us to ignore these parts of the language in the rest of our treatment of C11.

#### 3.0.1 Consume accesses

The formal C11 model we saw in Section 2.3.3 did not include CONSUME. Remember, a CONSUME read is supposed to order the store it reads from (provided it is at least release) with any read that has a data or address dependency on it. The problem is how to define such dependencies. In the standard, it is done syntactically. As a result there is a dependency between the two loads in the following code:

```

r = x.load(consume);

y = *(z+r-r);

```

but there is naturally no dependency between them in the following:

```

r = x.load(consume);

y = *z;

```

Any optimising compiler will transform the first fragment into the second one. Since there is no longer a dependency, the compiler must now introduce a fence before the second read on ARM and Power to prevent the processor from reordering the two reads. But knowing this would require the compiler to track every dependency in the program throughout the compilation pipeline. In particular, as dependencies are not necessarily local, it would break modular compilation. As a consequence, compilers just insert a fence every time on ARM/Power, treating consume as the (less efficient in theory) acquire. Several proposals have been made to improve this situation [McK16] and are under discussion by the C++ standards committee.

As the presence of CONSUME significantly complicates the model (for example it makes hb not transitive), and it is not usefully implementable, we will ignore it in the rest of this thesis.

#### 3.0.2 SC fences

The semantics of SC fences is also problematic, as despite their name they cannot restore full sequential consistency. Consider for example the IRIW example (Figure 2.3). If all the accesses are SC, then only the sequentially consistent outcomes can happen. But if the accesses are all RLX, no amount of SC fences can prevent the non-sequentially consistent outcome. This can be seen by a look at the axioms specific to SC fences:

- SCFences1, SCFences5, SCFences6 do not apply as they require a SC write;

- SCFences2 does not apply as it requires a SC read;

- SCFences3 only means that any SC fence sb after the writes must also be sc after any fence between the reads;

- SCFences4 does not apply as it requires two writes to the same location, one with a SC fence after it and the other with one before it.

This is unlikely to have been intended by the standards authors, as SC fences are supposed to be the strongest form of synchronisation, and their implementation on all platforms actually prevent the IRIW anomalous behaviour. For this reason, and because of their complexity, we have also decided to ignore SC fences in our treatment of C11.

## 3.1 Sanity properties

Now that we have identified a useful subset of C11, it is natural to check whether it has the properties we expect.

#### 3.1.1 Weakness of the SCReads axiom

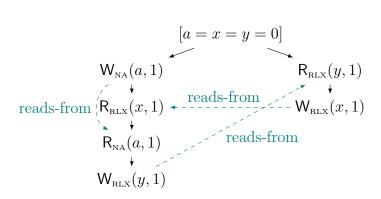

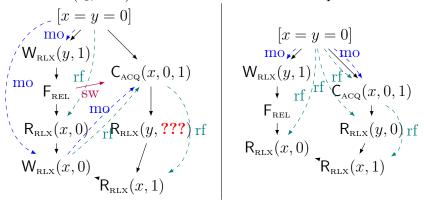

One desirable property of a memory model is that adding synchronisation to a program introduces no new behaviour (other than deadlock). We have seen that RLX is supposed to be the weakest memory attribute, and SC the strongest. So it should always be sound to replace a RLX access by a SC one. Unfortunately, it is not correct in C11 as it stands. Consider the example in Figure 3.1.

Coherence of the relaxed loads in the final thread forces the mo-orderings to be as shown in the execution on the bottom of the figure. Now, the question is whether the SC-load can read from the first store to x and return r=1. In the program as shown, it cannot, because that store happens before the x.store(2,SC) store, which is the immediate sc-preceding store to x before the load. If, however, we also make the x.store(3,RLX) be sequentially consistent, then it becomes the immediately sc-preceding store to x, and hence reading r=1 is no longer blocked. The SCReads axiom places an odd restriction on where a sequentially consistent read can read from. The problem arises from the case where the source of the read is a non SC write. In this case, the axiom forbids that write to happen before the immediately sc-preceding write to the same location. It may, however, happen before an earlier write in the sc order.

We propose to strengthen the SCReads axiom by requiring there not to be a happens before edge between rf(b) and any same-location write sc-prior to the read, as follows:

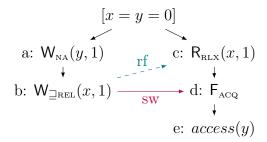

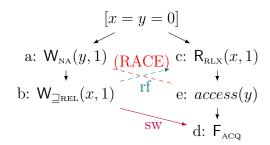

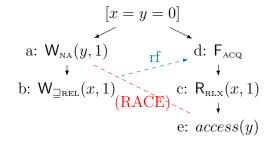

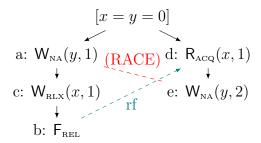

$$\forall a,b. \ rf(b) = a \land \mathsf{isSC}(b) \implies \mathsf{imm}(\mathsf{scr},a,b) \lor (\neg \mathsf{isSC}(a) \land \nexists x. \ \mathsf{hb}(a,x) \land \mathsf{scr}(x,b)) \tag{SCReads'}$$